# Surface passivation of n-GaN by nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> films

Choelhwyi Bae, Cristiano Krug, and Gerald Lucovsky<sup>a)</sup>

Department of Physics, North Carolina State University, Raleigh, North Carolina 27695-8202

Arpan Chakraborty and Umesh Mishra

Department of Electrical and Computer Engineering, University of California, Santa Barbara, California 93106

(Received 22 March 2004; accepted 24 May 2004)

The electrical characteristics of n-GaN/nitrided-thin-Ga $_2$ O $_3$ /SiO $_2$  and n-GaN/Si $_3$ N $_4$  metal-insulator-semiconductor (MIS) capacitors have been compared, and the work-function difference  $\phi_{\rm ms}$  and effective dielectric-fixed charge density  $Q_{\rm f,eff}$  have been determined. Oxide samples showed lower interface trap level density  $D_{\rm it}$ , lower leakage current, and better reproducibility compared to the nitride samples. The superior properties of the oxide samples are partially attributed to the nitrided-thin-Ga $_2$ O $_3$  layer ( $\sim$ 0.6-nm-thick).  $\phi_{\rm ms}$  and  $Q_{\rm f,eff}$  were determined, respectively, as 0.13 V and  $1.0\times10^{12}~q$  cm $^{-2}$  in oxide and 0.27 V and  $-3.6\times10^{11}~q$  cm $^{-2}$  in nitride samples using flatband voltage versus dielectric thickness data. True dielectric-fixed charge density and location of the major amount of fixed charge are discussed based on  $Q_{\rm f,eff}$ ,  $D_{\rm it}$ , and spontaneous polarization of n-GaN. © 2004 American Institute of Physics. [DOI: 10.1063/1.1772884]

#### I. INTRODUCTION

Gallium nitride/insulator interfaces have been investigated for application in GaN-based metal-insulator-semiconductor field effect transistors (MISFETs) and AlGaN/GaN high electron mobility transistors (HEMTs). <sup>1-3</sup> Many researchers have reported promising *n*-GaN/insulator interfaces showing a reduced interface trap level density  $D_{\rm it}$  as compared to MIS structures on other compound semiconductors (Ref. 1 and references therein). Among the promising insulating materials on GaN—mainly formed by plasma-assisted amorphous film deposition, epitaxial film growth, and oxidation of the GaN surface—SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> are potentially the most valuable as they have supported the Si-based MIS device industry.

The electrical properties reported for  $n\text{-}\mathrm{GaN/SiO}_2$  and  $n\text{-}\mathrm{GaN/Si}_3\mathrm{N}_4$  structures depend on GaN surface preparation and insulating film deposition method and gave rise to controversy concerning Fermi level pinning at the  $n\text{-}\mathrm{GaN/SiO}_2$  interface (Ref. 1 and references therein). When the oxide layer is formed by deposition rather than oxidation of the substrate, the cleaning method of the GaN surface is crucial for a reproducible interface featuring low  $D_{it}$ , because that very surface, buried under the deposited layer, becomes the GaN/dielectric interface. While the investigated and established *in situ* cleaning methods of the GaN surface have been successfully applied for surface studies of GaN and metal contacts in ultrahigh vacuum (UHV), most dielectrics in GaN-based MIS structures have been deposited after ex situ wet chemical treatment.

Ex situ or in situ removal of the air-grown native oxide on GaN does not guarantee the absence of an interfacial oxide in the n-GaN/SiO $_2$  structure because the presence of oxidant and excitation during processing very often leads to parasitic oxide growth on the substrate surface. During

plasma-assisted  $SiO_2$  deposition, a  $N_2$ -plasma-treated, nearly oxygen-free (oxygen coverage below 0.1 monolayer) n-GaN substrate was slightly consumed by plasma-activated oxygen species that diffused through the thickening  $SiO_2$  layer and oxidized the underlying substrate; online Auger-electron spectroscopy (AES) indicated a  $\sim$ 0.7-nm-thick subcutaneous oxide. Hashizume et al. ascribed poor capacitance-voltage (C-V) characteristics of  $GaN/SiO_2$  structures to unexpected and uncontrollable oxidation of the GaN surface during plasma-assisted  $SiO_2$  deposition. Interface defects in  $GaN/SiO_2$  MIS structures thus depend (among other factors) on the uncontrolled formation of interfacial gallium oxide during  $SiO_2$  deposition and postdeposition annealing steps.

The GaN/Si<sub>3</sub>N<sub>4</sub> structure has been the first choice when substrate oxidation is to be completely avoided. In GaN/Si<sub>3</sub>N<sub>4</sub> MIS capacitors (MIS-Cs), reduced  $D_{it}$  was obtained by a NH<sub>4</sub>OH cleaning followed by electron cyclotron resonance (ECR) N<sub>2</sub>-plasma treatment.<sup>3</sup> However, Si<sub>3</sub>N<sub>4</sub> appears to be a worse candidate than SiO<sub>2</sub> to gate dielectric due to trap levels in the lower half of the band gap as well as a small band offset with respect to GaN. Moreover, the n-GaN/Si<sub>3</sub>N<sub>4</sub> interface does show a small amount of residual gallium oxide (oxygen coverage below 0.5 monolayer) after a conventional wet cleaning followed by nitride deposition.<sup>5</sup>

Parasitic oxidation of GaN during plasma-assisted SiO<sub>2</sub> deposition has been prevented by intentional plasma-assisted oxidation of the substrate prior to dielectric deposition. 4 Such two-step process at 300 °C—(i) remote-plasma-assisted oxi-(RPAO) form an interfacial dation to (~0.6 nm thick) and (ii) remote-plasma-enhanced chemicalvapor deposition (RPECVD) to deposit SiO<sub>2</sub>—significantly reduced interfacial trapping as compared to single-step SiO<sub>2</sub> deposition. 4 The RPAO process at low temperature also provides in situ surface cleaning, e.g., reducing the level of residual carbon.

a)Electronic mail: gerry\_lucovsky@ncsu.edu

Of relevance to the electrical characterization of Algated MIS structures on n-GaN, the metal-semiconductor work-function difference  $\phi_{\rm ms}$  has been chosen as 0 V by assuming that the work function of Al and n-GaN are both 4.1 eV. Theoretical C-V curves for Al-gated n-GaN MIS-Cs have been drawn under that assumption. Although an accurate value of  $\phi_{\rm ms}$  must be known to determine the dielectric-fixed charge density  $Q_{\rm f}$  and little is known about the work function of GaN, there has been no effort to measure  $\phi_{\rm ms}$  for Al-gated MIS structures on n-GaN.

Assuming negligible dielectric-trapped charge density  $Q_{\rm ot}$  and mobile dielectric charge density  $Q_{\rm m}$  in a MIS structure, the flatband voltage  $V_{\rm FB}$  is given by  $^{7.8}$

$$V_{\rm FB} = \phi_{\rm ms} - \frac{Q_{\rm f} + Q_{\rm it}(\psi_{\rm s}) + Q_{\rm pol}}{C_{\rm ox}} = \phi_{\rm ms} - \frac{Q_{\rm f,eff}}{\varepsilon_{\rm ox}} t_{\rm ox}, \tag{1}$$

where  $Q_{\rm f}$  is the dielectric-fixed charge density,  $Q_{\rm it}$  is the interface-trapped charge density,  $\psi_{\rm s}$  is the semiconductor band bending,  $Q_{\rm pol}$  is the polarization charge density,  $C_{\rm ox}$  is the accumulation capacitance per unit area ( $C_{\rm ox} = \varepsilon_{\rm ox}/t_{\rm ox}$ , where  $\varepsilon_{\rm ox}$  is the permittivity of SiO<sub>2</sub> and  $t_{\rm ox}$  the equivalent SiO<sub>2</sub> thickness of the dielectric), and  $Q_{\rm f,eff}$  is the effective dielectric-fixed charge density. After measurement of  $V_{\rm FB}$  as a function of  $t_{\rm ox}$ ,  $\phi_{\rm ms}$ , and  $Q_{\rm f,eff}$  can be obtained from a linear fit to the experimental data; the intercept at the  $V_{\rm FB}$  axis is  $\phi_{\rm ms}$ , and the slope is  $-Q_{\rm f,eff}/\varepsilon_{\rm ox}$ . If  $Q_{\rm f,eff}$  results from different types of charging, possible compensation effects must be considered to extract  $Q_{\rm f}$ . In particular,  $Q_{\rm pol}$  has been ignored in the analysis of MIS-Cs on GaN.

In their wurtzite structure, group III nitrides show spontaneous polarization along the [0001] direction, which induces bound surface/interface charges and gives rise to a strong internal electric field. The spontaneous polarization in GaN leads to a negative-bound charge at the Ga face and a positive-bound charge at the N face. Epitaxial GaN layers grown by metal organic chemical-vapor deposition (MOCVD), as in this work, are typically Ga face. The theoretical value for the spontaneous polarization  $P_{\rm sp}$  of GaN is -0.029 C m<sup>-2</sup>, corresponding to a bound charge density of  $-1.73 \times 10^{13} q \text{ cm}^{-2}$  (where q is the elementary charge,  $1.6022 \times 10^{-19}$  C) at the Ga face. Piezoelectric polarization, which occurs in group III nitrides in addition to the spontaneous polarization, can be neglected if the GaN layer is above a critical thickness. In most previous reports on Algated n-GaN/SiO<sub>2</sub> MIS structures, the measured  $V_{\rm FB}$  is close to 0 V, and the reported  $Q_f$  is on the order of  $10^{11} q \text{ cm}^{-2}$ . This indicates that  $Q_{\rm pol}$  has been ignored despite its recognized and key effect in GaN/AlGaN heterostructures, because neutralization of the theoretical negative-bound charge requires ~100 times higher positive-charge density. Matocha et al. reported on  $Q_{pol}$  in n-GaN-based MIS structures. An observed positive shift of  $V_{FB}$  with increasing temperature was attributed to changes in  $Q_{pol}$ ; however, there was no consideration of  $Q_{\mathrm{pol}}$  itself. In the Al/SiO<sub>2</sub>/GaN/Al<sub>0.4</sub>Ga<sub>0.6</sub>N/GaN heterojunction MIS structure studied by Chen *et al.*,  $^{10}$  a wide *C-V* hysteresis window and a positive  $V_{\mathrm{FB}}$  shift corresponding to a charge density of  $-2.9 \times 10^{12} \ q \ \mathrm{cm}^{-2}$  were attributed to  $Q_{\mathrm{pol}}$ .

The surface passivation of AlGaN is emerging as an important issue in AlGaN/GaN (HEMT) applications. Frequency-dependent current degradation attributed to trap levels between gate and drain was almost eliminated in devices incorporating  $\mathrm{Si}_3\mathrm{N}_4$  or  $\mathrm{SiO}_2$ . Also, increased charge density in two-dimensional electron gases (2DEGs) was obtained by surface passivation of AlGaN using  $\mathrm{Si}_3\mathrm{N}_4$  and  $\mathrm{SiO}_2$  layers. Although the analysis of AlGaN-based MIS structures can be expected to be more complex than that of their GaN counterparts, it seems to be clear that the latter constitutes the basic research tool to understand the former.

We report the electrical characteristics of Al-gated n-GaN/nitrided-thin  $Ga_2O_3/SiO_2$  and n-GaN/ $Si_3N_4$  MIS-Cs as determined by C-V, ac conductance, and current-voltage (I-V) measurements. For conciseness, we refer to these structures as "SiO<sub>2</sub>" and "Si<sub>3</sub>N<sub>4</sub>" samples. SiO<sub>2</sub> samples feature a three-step process designed for optimal interface formation—RPAO followed by remote-plasma-assisted nitridation (RPAN) and SiO<sub>2</sub> deposition—whereas Si<sub>3</sub>N<sub>4</sub> samples feature the conventional single-step dielectric deposition on wet-etched substrate. We determine  $D_{\rm it}$ ,  $\phi_{\rm ms}$ , and  $Q_{\rm f,eff}$ , for both sets of samples, discuss the results based on interface structure, and consider the effect of  $Q_{\rm pol}$  on our findings.

## II. EXPERIMENTAL PROCEDURE

A homoepitaxial Fe-doped insulating GaN/unintentionally doped GaN/Si-doped GaN structure was grown on sapphire by MOCVD. The thickness of the Si-doped GaN epilayer was  $\sim 1~\mu m$ , and its bulk carrier density was  $3.3\times 10^{17}~\rm cm^{-3}$ . The *n*-GaN substrates were etched in NH<sub>4</sub>OH/H<sub>2</sub>O 1:5 solution at 80 °C for 15 min prior to introduction in the processing tool.

For the  ${\rm SiO_2}$  samples, the as-loaded n-GaN substrate was oxidized by remote  ${\rm O_2/He}$  plasma at 0.3 Torr for 30 s to form a thin superficial  ${\rm Ga_2O_3}$  layer, which was then nitrided by remote  ${\rm N_2/He}$  plasma at 0.3 Torr for 90 s.  ${\rm SiO_2}$  films were deposited by RPECVD using  ${\rm SiH_4}$  (2% in He) and an  ${\rm O_2/He}$  gas mixture at 0.3 Torr.  $^{4.5,14,15}$  For the  ${\rm Si_3N_4}$  samples, the dielectric was directly deposited on wet-etched GaN by RPECVD using  ${\rm SiH_4}$  (2% in He) and an  ${\rm N_2/He}$  gas mixture at 0.2 Torr.  $^{14}$  In all remote plasma processing, the substrate temperature was 300 °C and radio frequency (rf) power was 30 W at 13.56 MHz.

After  ${\rm SiO_2}$  or  ${\rm Si_3N_4}$  deposition, the samples were rapid-thermal annealed at 900 °C for 30 s in Ar atmosphere. A 300-nm-thick Al layer was evaporated onto the samples and defined by a conventional lithographic process. Postmetallization annealing (PMA) was performed at 400 °C for 30 min in forming gas ( ${\rm N_2/H_2}$ ). The electrical properties of MIS-Cs on *n*-GaN were investigated using HP 4284A and 4140B meters. The area of the devices under test was  $(1-4)\times 10^{-4}~{\rm cm^2}$ .

## III. RESULTS AND DISCUSSION

### A. Interface trap level density

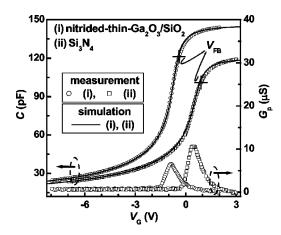

Figure 1 displays measured and simulated C-V characteristics of (i) a  $SiO_2$  and (ii) a  $Si_3N_4$  sample. Contrary to their  $SiO_2$  counterparts,  $Si_3N_4$  samples showed a large run-

FIG. 1. Measured and simulated C-V curves for Al-gated (i)  $n\text{-}GaN/\text{nitrided-thin-}Ga_2O_3/\text{Si}O_2$  and (ii)  $n\text{-}GaN/\text{Si}_3N_4$  MIS-Cs at 25 °C and 1 MHz;  $t_{ox}$  and  $V_{FB}$  are (i) 9.4 nm and -0.4 V and (ii) 11.4 nm and 0.9 V, respectively. Also shown is parallel conductance.

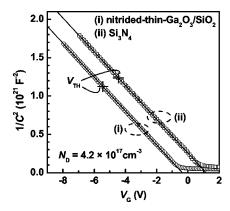

to-run variation. Optimal Si<sub>3</sub>N<sub>4</sub> samples were chosen for comparison with SiO<sub>2</sub> in this article. The equivalent SiO<sub>2</sub> thicknesses  $t_{ox}$  are (i) 9.4 and (ii) 11.4 nm. C-V curves were acquired at 1 MHz, at room temperature, in the dark, and with the gate voltage  $V_G$  being swept from positive to negative. In the evaluation of expressions for the theoretical C - V curves, <sup>7,16</sup> the same fundamental constants as in a previous report<sup>6</sup> were used. Because MIS-Cs on the wide-bandgap n-GaN showed deep depletion instead of inversion, the net donor concentration  $N_{\rm D}$  in the semiconductor substrate was obtained as  $4.2 \times 10^{17}$  cm<sup>-3</sup> for both samples from data fitting to the partial range of the C-V characteristics in which  $1/C^2$ -V is linear, as shown in Fig. 2. Simulated ideal (i.e., without considering oxide or interface defects) C-V curves were shifted along the voltage axis until they showed good agreement with the measured data.

The C-V data obtained from the  $\mathrm{Si}_3\mathrm{N}_4$  sample shows larger deviation from the simulated curve. Discrepancies are attributed to stretch-out of the experimental data along the  $V_{\mathrm{G}}$  axis due to changes in the occupancy of interface states. In the negative  $V_{\mathrm{G}}$  direction starting at a point below  $V_{\mathrm{FB}}$ , the measured C-V data are intrinsically well described by the

FIG. 2. Plot of  $1/C^2$  versus  $V_{\rm G}$  data for Al-gated (i) n-GaN/nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> and (ii) n-GaN/Si<sub>3</sub>N<sub>4</sub> MIS-Cs. Net doping concentration  $N_D$  obtained from the slopes is  $4.2 \times 10^{17}$  cm<sup>-3</sup> for both samples. Threshold voltages  $V_{\rm TH}$  are (i) –5.3 V and (ii) –4.4 V. Both samples clearly show deep depletion below  $V_{\rm TH}$ . Symbols are experimental data, lines are fit to the data.

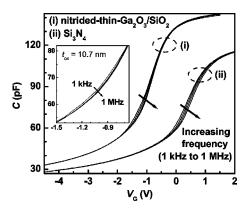

FIG. 3. Frequency dependence of the C-V characteristics of the MIS-Cs that originated Fig. 1. The inset displays data from the n-GaN/nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> MIS-C showing the lowest  $D_{it}$  among the samples fabricated.

simulated curves because interface states cannot follow changes in  $V_{\rm G}$  quasi-statically. The measured  $V_{\rm FB}$  is (i)  $-0.4~\rm V$  for the SiO $_2$  and (ii) 0.9 V for the Si $_3\rm N_4$  sample. Such  $V_{\rm FB}$  data is used in the next section to determine  $\phi_{\rm ms}$  and  $Q_{\rm f,eff}$ .

Figure 1 also shows the measured parallel conductance  $G_p$  for both  $\mathrm{SiO}_2$  and  $\mathrm{Si}_3\mathrm{N}_4$  samples, evidencing clear peaks of interface trap loss and negligible dielectric loss. The conductance peak of the  $\mathrm{Si}_3\mathrm{N}_4$  sample is about 1.5 times higher than that of the  $\mathrm{SiO}_2$  sample. Because these samples showed similar values of series resistance ( $\sim 200~\Omega$ ) and  $C_{\mathrm{ox}}$ ,  $D_{\mathrm{it}}$  is nearly proportional to the measured conductance peak height.

We refrain from estimating  $D_{it}$  using the Terman method. The  $N_D$  for n-GaN in MIS-Cs was obtained by fitting the measured C-V data. In this case, stretch-out due to changes in the occupancy of interface traps can be misinterpreted as increased doping concentration, also leading to the underestimation of  $D_{it}$  as determined by the Terman method. The high-low frequency C-V and ac conductance methods  $^{16}$  were used to extract a more reliable  $D_{it}$ , within their limitations when applied to n-GaN MIS devices.  $^{18,19}$

Figure 3 shows the frequency dependence (1, 10, 100 kHz and 1 MHz) of the C-V characteristics of the (i)  $\mathrm{SiO}_2$  and (ii)  $\mathrm{Si}_3\mathrm{N}_4$  samples that originated Fig. 1. The inset displays C-V characteristics of the sample showing the lowest interface trap level density among the  $\mathrm{SiO}_2$  samples fabricated. In the high-low frequency C-V method,  $D_{\mathrm{it}}$  as a function of gate voltage is calculated from  $^{16}$

$$D_{\rm it} = \frac{C_{\rm ox}}{q} \left( \frac{C_{\rm lf}/C_{\rm ox}}{1 - C_{\rm lf}/C_{\rm ox}} - \frac{C_{\rm hf}/C_{\rm ox}}{1 - C_{\rm hf}/C_{\rm ox}} \right),\tag{2}$$

where  $C_{\rm lf}$  is the capacitance measured at low frequency ( $f=1~{\rm kHz}$ ) and  $C_{\rm hf}$  is the capacitance measured at high frequency ( $f=1~{\rm MHz}$ ). In our samples, the actual  $D_{\rm it}$  is higher than estimated using this method because 1 kHz is not sufficiently low to allow the response of slow interface traps. The  $V_{\rm G}$  at which high- and low-frequency C-V curves show the maximum capacitance difference  $\Delta C_{\rm max}$  corresponds to an energy level at which  $D_{\rm it}$  can be extracted without severe underestimation. The extracted  $D_{\rm it}$  rapidly decreases below  $V_{\rm G}(\Delta C_{\rm max})$  because, as noted earlier,

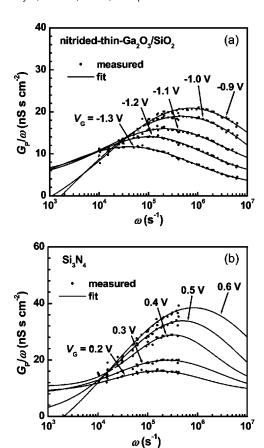

FIG. 4. Parallel conductance  $G_{\rm p}/\omega$  versus angular frequency  $\omega$  from (a) n-GaN/nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> and (b) n-GaN/Si<sub>3</sub>N<sub>4</sub> MIS-Cs. Points are experimental data; lines are Gaussian fit to the data.

interface states cannot follow changes in  $V_{\rm G}$  quasi-statically and thus become undetected. The  $D_{\mathrm{it}}$  from  $\Delta C_{\mathrm{max}}$  is 4  $\times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> at  $V_G$ =-1.1 V for the SiO<sub>2</sub> sample and 9  $\times 10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> at  $V_G$ =0.4 eV for the Si<sub>3</sub>N<sub>4</sub> sample. We present the energy distribution of  $D_{it}$  according to the highlow frequency method after considering ac conductance measurements.

Figure 4 displays parallel conductance  $G_{\rm p}/\omega$  versus angular frequency  $\omega = 2\pi f$  curves at selected gate voltages. From the graphically determined standard deviation of band bending  $\sigma_{\rm s}$  and universal function  $f_{\rm D}$  as a function of  $\sigma_{\rm s}$ , the  $D_{\rm it}$  of each sample was extracted using <sup>16</sup>

$$D_{\rm it} = \left(\frac{G_{\rm p}}{\omega}\right)_{\rm fp} [qf_{\rm D}(\sigma_{\rm S})]^{-1},\tag{3}$$

where  $f_p$  is the frequency corresponding to the peak value of  $G_{\rm p}/\omega$ . The determined values of  $f_{\rm D}$  were 0.18–0.20 for the

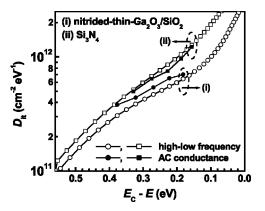

FIG. 5. Interface trap level density Dit for (i) n-GaN/nitrided-thin  ${\rm Ga_2O_3/SiO_2}$  and (ii)  $n{\rm -GaN/Si_3N_4}$  MIS-Cs as determined using the ac conductance and high-low frequency C-V methods.

$SiO_2$  and 0.19–0.24 for the  $Si_3N_4$  sample. The  $D_{it}$  from the ac conductance and high-low frequency C-V methods is shown in Fig. 5 as a function of energy relative to the GaN conduction band edge  $E_{\rm C}$ . The SiO<sub>2</sub> sample shows lower  $D_{\rm it}$ according to both methods in the whole energy interval under consideration. As noted earlier, Si<sub>3</sub>N<sub>4</sub> samples presented poor reproducibility; the result shown is from an optimal sample. For the SiO<sub>2</sub> sample that originated the inset in Fig. 3,  $D_{\rm it}$  from the high-low frequency C-V method at  $E_{\rm C}$ -E $\approx 0.3 \text{ eV}$  is  $1 \times 10^{11} \text{ cm}^{-2} \text{ eV}^{-1}$ ; the ac conductance method could not be used for this sample due to a small signal-tonoise ratio, as observed for an optimized SiO<sub>2</sub>/Si<sub>3</sub>N<sub>4</sub>/SiO<sub>2</sub> (ONO) structure on n-GaN. The rapidly decreasing  $D_{it}$  for both  $SiO_2$  and  $Si_3N_4$  samples at  $E_C-E>0.3$  eV  $\approx qV_{\rm G}(\Delta C_{\rm max})$  is not realistic, as discussed earlier.

Table I summarizes the parameters extracted from the electrical characterization of SiO<sub>2</sub> samples featuring various  $t_{\rm ox}$ . All MIS-Cs were fabricated under the same conditions, but the sample featuring  $t_{ox}$ =20.3 nm showed higher  $D_{it}$  and a significantly wider, positive hysteresis window as compared to the others. Implications will be noted in the following section.

## B. Dielectric-fixed charge density and metal-semiconductor work-function difference

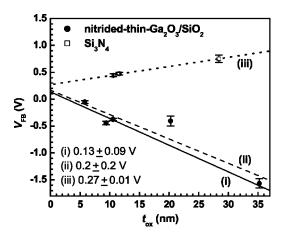

Figure 6 shows  $V_{\rm FB}$  versus  $t_{\rm ox}$  data for Al-gated [(i) and (ii)]  $SiO_2$  and (iii)  $Si_3N_4$  samples. For the  $SiO_2$  samples, linear fitting was performed (i) excluding and (ii) including the sample with  $t_{\rm ox}$ =20.3 nm;  $\phi_{\rm ms}$  and  $Q_{\rm f,eff}$  were thus determined as (i)  $0.13\pm0.09 \text{ V}$  and  $(1.0\pm0.1)\times10^{12} \text{ q cm}^{-2}$  and

TABLE I. Summary of parameters extracted from n-GaN/nitrided-thin-Ga2O3/SiO2 MIS-Cs featuring various  $t_{\rm ox}$ . The hysteresis window is reported at flatband capacitance, and minimum  $D_{\rm it}$  was obtained at  $E_{\rm C}$ -E $\approx$  0.3 eV using the high-low frequency C-V and the ac conductance (data in parentheses) methods.

| t <sub>ox</sub> (nm) | $N_{\rm D}$ $(10^{17}~{\rm cm}^{-3})$ | V <sub>FB</sub> (V) | <i>V</i> <sub>TH</sub> (V) | Hysteresis<br>window (V) | $D_{\rm it}$ (10 <sup>11</sup> cm <sup>-2</sup> eV <sup>-1</sup> ) |

|----------------------|---------------------------------------|---------------------|----------------------------|--------------------------|--------------------------------------------------------------------|

| 5.8                  | 4.0                                   | -0.02               | -4.34                      | -0.03                    | 3.3                                                                |

| 9.4                  | 4.2                                   | -0.46               | -5.43                      | -0.02                    | 4.3 (5.4)                                                          |

| 10.5                 | 4.0                                   | -0.39               | -5.36                      | -0.03                    | 2.0                                                                |

| 20.3                 | 3.9                                   | -0.43               | -7.17                      | 0.50                     | 8.5                                                                |

| 35.2                 | 4.1                                   | -1.50               | -10.72                     | -0.02                    | 6.3 (6.8)                                                          |

FIG. 6. Linear fits to flat band voltage  $V_{\rm FB}$  versus equivalent oxide thickness  $t_{\rm ox}$  data from n-GaN/nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> MIS-Cs [(i) excluding and (ii) including the point at 20.3 nm] and from (iii) n-GaN/Si<sub>3</sub>N<sub>4</sub> MIS-Cs. The displayed error bars are standard deviations of  $V_{\rm FB}$  measured for different capacitors on each sample. Standard deviations of  $t_{\rm ox}$  are below  $\pm 1\%$  of  $t_{\rm ox}$ .

(ii)  $0.2\pm0.2 \text{ V}$  and  $(1.0\pm0.2)\times10^{12} \ q \text{ cm}^{-2}$ , respectively. We note that for the proper extraction of  $\phi_{\text{ms}}$ , it is an essential requirement that all samples considered present the same amount of charge at the semiconductor-oxide interface. The sequential etching of  $\text{SiO}_2$  can be seen as an alternative method to produce samples with different  $t_{\text{ox}}$  satisfying the requirement of a constant amount of charge at the semiconductor-oxide interface.

To evaluate Al/n-GaN/Si<sub>3</sub>N<sub>4</sub> structures, samples with relatively low  $D_{\rm it}$  were chosen. Si<sub>3</sub>N<sub>4</sub> samples with high  $D_{\rm it}$  (mid- $10^{12}$  cm<sup>-2</sup> eV<sup>-1</sup>) showed more positive  $V_{\rm FB}$ , whose proper extraction was made difficult by significant electron trapping. Large positive  $V_{\rm FB}$  was also reported on nonoptimized n-GaN MIS structures with high  $D_{\rm it}$  using SiO<sub>2</sub> and ONO dielectrics. For the selected Si<sub>3</sub>N<sub>4</sub> samples with relatively low  $D_{\rm it}$ ,  $\phi_{\rm ms}$  and  $Q_{\rm f,eff}$  extracted from our data are  $0.27\pm0.01$  V and  $(-3.6\pm0.2)\times10^{11}$  q cm<sup>-2</sup>, respectively.

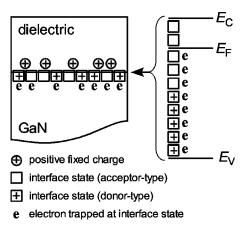

Focusing on  $Q_{\rm f,eff}$  results, Fig. 7 illustrates that in the case of a MIS-C on n-type substrate at  $V_{\rm FB}$ , most of the interface trap levels are occupied. We assume that interface traps at the upper (lower) half of the band gap are acceptor-(donor-) type. Acceptor-type (neutral when empty) interface traps below the Fermi energy  $E_{\rm F}$  appear as negative  $Q_{\rm it}$ , whereas acceptor-type interface traps above  $E_{\rm F}$  and donor-type (positive when empty) interface traps do not contribute to  $Q_{\rm it}$  because they are both neutral. Furthermore, we momentarily neglect  $Q_{\rm pol}$  in Eq. (1). Then

$$Q_{\rm f} = Q_{\rm f,eff} - Q_{\rm it,e} \approx Q_{\rm f,eff} + qD_{\rm it} \left[ \frac{E_{\rm g}}{2} - (E_{\rm C} - E_{\rm F}) \right],$$

(4)

where  $Q_{\rm it,e}$  is the interface-trapped charge density  $(Q_{\rm it,e} < 0)$  and  $E_{\rm g}$  is the band gap energy of GaN,  $E_{\rm C} - E_{\rm V}$ . Using  $Q_{\rm f,eff}$  reported earlier, taking  $D_{\rm it}$  from ac conductance results in Fig. 5 at  $E_{\rm C} - E_{\rm E} = 0.3$  eV and using  $E_{\rm C} - E_{\rm F} = 0.1$  eV,  $Q_{\rm f}$  becomes  $\sim 1.7 \times 10^{12}~q~{\rm cm}^{-2}$  in SiO<sub>2</sub> samples and  $\sim 5.5 \times 10^{11}~q~{\rm cm}^{-2}$  in Si<sub>3</sub>N<sub>4</sub> samples. Therefore, although SiO<sub>2</sub> samples present lower  $D_{\rm it}$  and better reproducibility than Si<sub>3</sub>N<sub>4</sub> samples, they apparently present higher dielectric

FIG. 7. Interface trap level configuration in an MIS structure on n-type substrate at  $V_{\rm FB}$ .

fixed charge density. We recall that all calculations shown earlier assume this fixed charge to be at the semiconductor/dielectric interface (as verified for the  $\mathrm{Si/SiO_2}$  system). If such charge density is distributed over the dielectric film thickness, the figures just presented for  $Q_{\mathrm{f,eff}}$  and  $Q_{\mathrm{f}}$  are overestimated. That could be the case for the  $\mathrm{Si_3N_4}$  samples (even though they have not been subjected to electrical stress before measurements). In the case of  $\mathrm{SiO_2}$  samples, we speculate that the major amount of fixed dielectric charge is located at the nitrided-thin- $\mathrm{Ga_2O_3/SiO_2}$  interface.

We now consider the possible effect of  $Q_{\rm pol}$  on  $Q_{\rm f}$ . The theoretical value of upward surface band bending at the Gaface of GaN is 3.4 V.<sup>20</sup> The experimentally obtained upward band bending is lower and dependent on the cleaning method of GaN via structural defects, surface states, and contamination causing Fermi level pinning or additional charge screening.<sup>20</sup> For example, Bermudez<sup>21</sup> found that practical n-GaN surfaces prepared by cleaning in aqueous NH<sub>4</sub>OH show an upward band bending of  $0.4\pm0.2$  V, less than the value of 0.9 V obtained after cleaning in UHV. Tracy et al., 22 who performed in situ chemical vapor cleaning (CVC), reported an upward band bending of  $\sim 0.3 \text{ V}$ . Consider n-GaN-based MIS structures showing a low density of donor-like surface states and negligible upward band bending, i.e.,  $D_{\rm it}$  on the order of  $10^{11}\,{\rm cm}^{-2}\,{\rm eV}^{-1}$  and  $V_{\rm FB}$  close to 0 V, as in the present work. One possible screening mechanism of  $Q_{pol}$  is positive  $Q_f$ . Including  $Q_{pol}$  corresponding to the theoretical  $P_{\rm sp}$  in (4) as per (1),  $Q_{\rm f}$  in our MIS structures could be as high as  $\sim 2 \times 10^{13} q \text{ cm}^{-2}$ . In SiO<sub>2</sub> samples, we suggest the Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface as the location of the major amount of positive  $Q_{\rm f}$ . The preparation of  $\textit{n-}GaN/nitrided-thin-}Ga_2O_3/Al_2O_3 \quad samples \quad is \quad underway.$ Lower Q<sub>f</sub> at the Ga<sub>2</sub>O<sub>3</sub>/Al<sub>2</sub>O<sub>3</sub> interface as compared to  $Ga_2O_3/SiO_2$  could lead to incomplete neutralization of  $Q_{pol}$ and appear as a significant positive shift of  $V_{\rm FB}$ .

We finally examine the possibility of  $Q_{\rm pol}$  screening due to the presence of hydrogen, a ubiquitous impurity. First-principles calculations indicate that the H<sup>-</sup> configuration is favored over H<sup>+</sup> and H<sup>0</sup> for hydrogen in GaN with  $E_{\rm F}$  close to  $E_{\rm C}$ , as in our substrate.<sup>23</sup> Therefore, H in n-GaN is not expected to screen  $Q_{\rm pol}$ . It has been established that interstitial atomic H is amphoteric at the Si/SiO<sub>2</sub> interface, inducing

a characteristic  $D_{\rm it}$  peak 0.2 eV above the Si midgap level. First-principles calculations indicate the H<sup>+</sup> configuration to be favored in SiO<sub>2</sub> for  $E_{\rm F}$ – $E_{\rm V}$ <3.5 eV. Si Given the available information on band alignment at the SiO<sub>2</sub>/GaN interface and  $E_{\rm F}$  in our substrate, it is unlikely that hydrogen in SiO<sub>2</sub> contributes to  $Q_{\rm pol}$  screening. We have no account of H-charge state behavior in nitrided-thin-Ga<sub>2</sub>O<sub>3</sub> or Si<sub>3</sub>N<sub>4</sub>. Charge configuration changes, as long as occurring for  $E_{\rm F}$  within the semiconductor band gap, should appear as  $D_{\rm it}$ . Such interface states, however, could be out of the energy range probed by standard measurement techniques.

Regarding  $\phi_{\rm ms}$ , we obtain 0.13 V from the SiO<sub>2</sub> samples, which is close to the 0 V assumed in most previous reports on  $n\text{-}\mathrm{GaN/SiO_2}$  MIS-Cs. An  $n\text{-}\mathrm{GaN/SiO_2}$  interface without detectable  $\mathrm{Ga_2O_3}$  was prepared by annealing GaN at 860 °C for 15 min in  $1.0\times10^{-4}$  Torr of NH<sub>3</sub> (CVC process), depositing an ultrathin Si sacrificial layer, and oxidizing it.<sup>27</sup> There is no report on metal-oxide-semiconductor (MOS) capacitors featuring such an  $n\text{-}\mathrm{GaN/SiO_2}$  interface without interfacial  $\mathrm{Ga_2O_3}$ . Using ultraviolet photoelectron spectroscopy (UPS) and x-ray photoelectron spectroscopy (XPS), the conduction band offset  $\Delta E_{\rm C}$  was deduced as 3.6 eV. If the work function of Al  $\phi_{\rm m}$  and the electron affinity of  $\mathrm{SiO_2}~\chi$  are taken as 4.1 and 1.1 eV, respectively,  $\phi_{\rm ms}$  for the direct  $n\text{-}\mathrm{GaN/SiO_2}$  MOS structure with Al gate should be close to -0.7 V, according to  $^7$

$$q\phi_{\rm ms} = \phi_{\rm m} - [\chi + \Delta E_{\rm C} + (E_{\rm C} - E_{\rm F})],$$

(5)

where  $E_{\rm C}-E_{\rm F}$  is again taken as  $\sim 0.1$  eV. Note that to keep up with common practice, we report  $\phi_{\rm ms}$  in electric potential and the quantities in the right-hand side of Eq. (5) in energy units.

In metallurgical junctions, partial charge transfer between interface states of the two materials results in interface dipoles. Our methodology to determine  $\phi_{

m ms}$  yields an effective value that incorporates any interface-dipole effects.<sup>28</sup> At n-GaN/dielectric interfaces, the interface dipole ranged from 1.3 to 2.0 V when  $SiO_2$ ,  $Si_3N_4$ , or  $HfO_2$  was used as a dielectric. <sup>26,27,29</sup> Although that is included (through  $\Delta E_C$ ) in the estimation above, the interface dipole between the Al gate and SiO<sub>2</sub> should make the effective  $\phi_{ms}$  higher (i.e., less negative or more positive) than -0.7 V. We therefore ascribe the difference between -0.7 V and our result of 0.13 V to the combined effect of interface dipoles (i) between Al and SiO<sub>2</sub> and (ii) involving the interfacial nitrided-thin Ga<sub>2</sub>O<sub>3</sub> in our samples. A more conclusive discussion will be possible after we determine (i)  $\phi_{

m ms}$  using Al-gated MIS-Cs featuring the direct n-GaN/SiO $_2$  interface and/or (ii)  $\Delta E_{\rm C}$  between *n*-GaN and nitrided-thin Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> using UPS and XPS.

Using n-GaN/Si<sub>3</sub>N<sub>4</sub> structures,  $\Delta E_{\rm C}$  for the direct interface has been determined<sup>27</sup> as 2.5 eV. Taking  $\chi$ =1.8 V in (6) to account for the electron affinity of Si<sub>3</sub>N<sub>4</sub> leads to  $\phi_{\rm ms}$   $\approx$  -0.3 V for Al-gated samples. Again, the difference between -0.3 V and our result of 0.27 V should be due to the combined effect of interface dipoles (i) between Al and Si<sub>3</sub>N<sub>4</sub> and (ii) involving parasitic interfacial gallium oxide in our Si<sub>3</sub>N<sub>4</sub> samples. Such interface dipoles must also account for the difference in  $\phi_{\rm ms}$  as obtained from SiO<sub>2</sub> and Si<sub>3</sub>N<sub>4</sub> samples (0.13 and 0.27 V, respectively). With interface di-

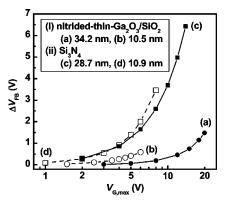

FIG. 8. Flatband voltage shift  $\Delta V_{\rm FB}$  as a function of maximum gate bias  $V_{\rm G,max}$  as determined for (i)  $n\text{-GaN/nitrided-thin-Ga}_2\mathrm{O}_3/\mathrm{SiO}_2$  and (ii)  $n\text{-GaN/Si}_3\mathrm{N}_4$  MIS-Cs.

poles properly taken into account,  $\phi_{ms}$  should be independent of dielectric as its textbook definition requires.

## C. Electron trapping and electrical conduction

C-V characteristics of n-GaN MIS structures have been measured (before and in this study) by sweeping  $V_G$  from positive to negative. Substrate electron injection into dielectric traps due to the starting positive bias would cause positive  $\Delta V_{\rm FB}$ . As shown in Fig. 8, that is indeed observed, with  $Si_3N_4$  samples showing several times larger  $\Delta V_{FB}$  than  $SiO_2$ samples under comparable maximum (starting) positive bias  $V_{\rm G,max}$ . For an Si<sub>3</sub>N<sub>4</sub> sample showing  $t_{\rm ox} \approx 11$  nm,  $N_{\rm D}$  obtained from  $1/C^2-V$  data increased from 4.2 to 4.4  $\times 10^{17}$  cm<sup>-3</sup> for  $V_{\rm G,max}$ =0 to 6 V due to the emission of trapped electrons. When  $V_{G,max}$  was reduced from 3 to 0 V,  $V_{\rm FR}$  and hysteresis window were reduced from 0.9 to 0.5 V and from 0.1 to 0.02 V, respectively. Significant electron trapping in our Si<sub>3</sub>N<sub>4</sub> samples is ascribed to an elevated density of traps in the bulk Si<sub>3</sub>N<sub>4</sub> film and a small conduction band offset between Si<sub>3</sub>N<sub>4</sub> and GaN. As for SiO<sub>2</sub> samples, electron trapping should take place mostly at or near the interface with GaN, in trap levels out of our detection range. The absence of bulk electron traps in plasma-enhanced chemical vapor deposition (PECVD) SiO<sub>2</sub> can be inferred from its demonstrated performance on Si substrates.

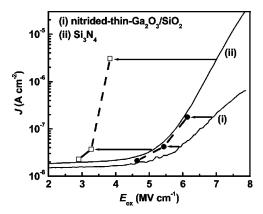

Figure 9 displays gate current density J versus effective oxide field  $E_{\rm ox}$  for (i) SiO<sub>2</sub> ( $t_{\rm ox}$ =10.7 nm) and (ii) Si<sub>3</sub>N<sub>4</sub> ( $t_{\rm ox}$ =10.5 nm) samples under a  $V_{\rm G}$  sweep rate of 0.05 V s<sup>-1</sup>.  $E_{\rm ox}$  is given by

$$E_{\rm ox} = V_{\rm ox}/t_{\rm ox} = (V_{\rm G} - V_{\rm FB} - \psi_{\rm s})/t_{\rm ox},$$

(6)

in which  $V_{\rm ox}$  is the voltage drop across the dielectric film and  $\psi_{\rm s}$  is the semiconductor band bending, negligible under accumulation. The solid lines in Fig. 9 result from using  $V_{\rm FB}$  as (i) -0.35 V for the SiO<sub>2</sub> and (ii) 0.5 V for the Si<sub>3</sub>N<sub>4</sub> sample. These  $V_{\rm FB}$  were obtained from C-V curves showing negligible  $\Delta V_{\rm FB}$  induced by positive gate bias. The dashed lines take into account  $\Delta V_{\rm FB}$  data from Fig. 8. Whereas J for the SiO<sub>2</sub> sample remains in the displacement current range up to  $E_{\rm ox} \approx 4.5$  MV cm<sup>-1</sup>, the onset of significant leakage through Si<sub>3</sub>N<sub>4</sub> appears at  $E_{\rm ox} \approx 3$  MV cm<sup>-1</sup>. Note that the principal breakdown mode of both samples is extrinsic, occurring be-

FIG. 9. Current density J versus electric field  $E_{\rm ox}$  from (i)  $n\text{-GaN/nitrided-thin-Ga}_2\text{O}_3/\text{SiO}_2$  ( $t_{\rm ox}$ =10.7 nm) and (ii)  $n\text{-GaN/Si}_3\text{N}_4$  ( $t_{\rm ox}$ =10.5 nm) MIS-Cs. Solid lines are obtained by using  $V_{\rm FB}$  as (i) -0.35 V and (ii) 0.5 V; dashed lines are obtained by applying  $V_{\rm FB}$  shown in Fig. 8.

low 10 MV cm<sup>-1</sup>, and  $J-E_{\rm ox}$  data were chosen among 20 breakdown events.

At present, there are few available reports on  $J-E_{\rm ox}$ characteristics of MIS structures on n-GaN and SiO2 or Si<sub>3</sub>N<sub>4</sub>. For an ONO structure on n-GaN, the tunneling current was observed above 6 MV cm<sup>-1</sup>, and the extracted barrier height from the Fowler-Nordheim model was 2.3 eV. For Si<sub>3</sub>N<sub>4</sub> on *n*-GaN,  $J \approx 1 \times 10^{-5}$  A cm<sup>-2</sup> at 6 MV cm<sup>-1</sup>, and the conduction-band offset energy was deduced as 0.5 eV based on XPS data.<sup>30</sup> Ga<sub>2</sub>O<sub>3</sub> (20-80 nm)/SiO<sub>2</sub> (20 nm) insulator stacks analyzed under the Frenkel-Poole model yielded a forward breakdown field  $2.64 - 3.56 \text{ MV cm}^{-1}$ and a barrier height of 0.63-1.21 eV.31 Our results lie well within the general framework. A detailed discussion of electrical conduction in our samples, including band offset energy determination will be possible after we obtain improved electron trapping and breakdown behavior.

## **IV. CONCLUSIONS**

We have compared Al-gated *n*-GaN/nitrided-thin Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> and *n*-GaN/Si<sub>3</sub>N<sub>4</sub> MIS-Cs using *C-V*, ac conductance, and *I-V* measurements. On wet-cleaned *n*-GaN surfaces, nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> yielded reduced density of interface defects, electron trapping, and leakage current as compared to Si<sub>3</sub>N<sub>4</sub>. Reproducibility also distinguishes *n*-GaN/nitrided-thin-Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> from *n*-GaN/Si<sub>3</sub>N<sub>4</sub> structures. Without separate *in situ* surface cleaning at high temperature, the RPAO-RPAN process provides excellent control of ultrathin interfacial layers that passivate the GaN substrate.

From linear fittings to  $V_{\rm FB}$  versus  $t_{\rm ox}$  data,  $\phi_{\rm ms}$  and  $Q_{\rm f,eff}$  were determined as 0.13 V and  $1.0\times10^{12}~q~{\rm cm}^{-2}$  for  ${\rm SiO_2}$  and as 0.27 V and  $-3.6\times10^{11}~q~{\rm cm}^{-2}$  for  ${\rm Si_3N_4}$  samples. The  $\phi_{\rm ms}$  was compared to estimates obtained from spectroscopic data and discussed in terms of interface dipole effects.

Both  $Q_{\rm f,eff}$  and  $D_{\rm it}$  were used to estimate  $Q_{\rm f}$ , and a possible contribution of  $Q_{\rm pol}$  was considered. Most of the dielectric-fixed charge in SiO<sub>2</sub> samples should be located at the Ga<sub>2</sub>O<sub>3</sub>/SiO<sub>2</sub> interface, whereas in Si<sub>3</sub>N<sub>4</sub> it could be distributed over the insulating film. At comparable  $t_{\rm ox}$ , SiO<sub>2</sub> samples provide lower leakage current and higher breakdown field.

#### **ACKNOWLEDGMENTS**

This research is supported by the ONR, AFOSR, SRC, and i-Sematech/SRC Front End Processes Center.

- <sup>1</sup>S. J. Pearton, F. Ren, A. P. Zhang, and K. P. Lee, Mater. Sci. Eng., R. **30**, 55 (2000).

- <sup>2</sup>R. Vetury, N. Q. Q. Zhang, S. Keller, and U. K. Mishra, IEEE Trans. Electron Devices **48**, 560 (2001).

- <sup>3</sup>T. Hashizume, S. Ootomo, T. Inagaki, and H. Hasegawa, J. Vac. Sci. Technol. B 21, 1828 (2003).

- <sup>4</sup>C. Bae and G. Lucovsky, J. Vac. Sci. Technol. A (to be published).

- <sup>5</sup>C. Bae and G. Lucovsky, Surf. Sci. **532**, 759 (2003).

- <sup>6</sup>H. C. Casey, G. G. Fountain, R. G. Alley, B. P. Keller, and S. P. DenBaars, Appl. Phys. Lett. **68**, 1850 (1996).

- <sup>7</sup>D. K. Schroder, *Semiconductor Material and Device Characterization*, 2nd ed. (Wiley, New York, 1998).

- <sup>8</sup>K. Matocha, T. P. Chow, and R. J. Gutmann, IEEE Electron Device Lett. 23, 79 (2002).

- <sup>9</sup>F. Bernardini, V. Fiorentini, and D. Vanderbilt, Phys. Rev. B **56**, 10024 (1997).

- <sup>10</sup>P. Chen, S. J. Chua, W. D. Wang, D. Z. Chi, Z. L. Miao, and Y. D. Zheng, J. Appl. Phys. **94**, 4702 (2003).

- <sup>11</sup>B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, IEEE Electron Device Lett. 21, 268 (2000).

- <sup>12</sup>T. R. Prunty, J. A. Smart, E. M. Chumbes, B. K. Ridley, L. F. Eastman, and J. R. Shealy, *Proceedings of the 2000 IEEE/Cornell Conference on High Performance Devices* (2000), p. 208.

- <sup>13</sup>X. Z. Dang, E. T. Yu, E. J. Piner, and B. T. McDermott, J. Appl. Phys. **90**, 1357 (2001).

- <sup>14</sup>G. Lucovsky, IBM J. Res. Dev. **43**, 301 (1999).

- <sup>15</sup>C. Bae and G. Lucovsky, J. Vac. Sci. Technol. A (to be published).

- <sup>16</sup>E. H. Nicollian and J. R. Brews, MOS (Metal Oxide Semiconductor) Physics and Technology (Wiley, New York, 1982).

- <sup>17</sup>J. A. Cooper, Phys. Status Solidi A **162**, 305 (1997).

- <sup>18</sup>B. Gaffey, L. J. Guido, X. W. Wang, and T. P. Ma, IEEE Trans. Electron Devices 48, 458 (2001).

- <sup>19</sup>J. P. Ibbetson, P. T. Fini, K. D. Ness, S. P. DenBaars, J. S. Speck, and U. K. Mishra, Appl. Phys. Lett. **77**, 250 (2000).

- <sup>20</sup>U. Karrer, O. Ambacher, and M. Stutzmann, Appl. Phys. Lett. 77, 2012 (2000).

- <sup>21</sup>V. M. Bermudez, J. Appl. Phys. **80**, 1190 (1996).

- <sup>22</sup>K. M. Tracy, W. J. Mecouch, R. F. Davis, and R. J. Nemanich, J. Appl. Phys. **94**, 3163 (2003).

- <sup>23</sup>J. Neugebauer and C. G. Van de Walle, Phys. Rev. Lett. **75**, 4452 (1995).

- <sup>24</sup>P. E. Blöchl and J. H. Stathis, Phys. Rev. Lett. **83**, 372 (1999).

- <sup>25</sup>A. Yokozawa and Y. Miyamoto, Phys. Rev. B **55**, 13783 (1997).

- <sup>26</sup>T. E. Cook, C. C. Fulton, W. J. Mecouch, K. M. Tracy, R. F. Davis, E. H. Hurt, G. Lucovsky, and R. J. Nemanich, J. Appl. Phys. 93, 3995 (2003).

- <sup>27</sup>T. E. Cook, C. C. Fulton, W. J. Mecouch, R. F. Davis, G. Lucovsky, and R. J. Nemanich, J. Appl. Phys. **94**, 3949 (2003).

- <sup>28</sup>H. Z. Massoud, J. Appl. Phys. **63**, 2000 (1988).

- E. Massoud, J. Appl. Phys. 63, 2000 (1766).

E. Cook, C. C. Fulton, W. J. Mecouch, R. F. Davis, G. Lucovsky, and R. J. Nemanich, J. Appl. Phys. 94, 7155 (2003).

- <sup>30</sup>K. M. Chang, C. C. Cheng, and C. C. Lang, Solid-State Electron. **46**, 1309 (2002)

- <sup>31</sup>C. T. Lee, H. Y. Lee, and H. W. Chen, IEEE Electron Device Lett. **24**, 54