#### ABSTRACT

YUAN, SHOUGANG. Bandwidth-Efficient Secure Memory Designs for GPUs. (Under the direction of Dr. Huiyang Zhou).

Wide adoption of cloud computing makes privacy and security a primary concern. Although recent CPUs have integrated secure memory architecture, such support is still missing for GPUs, a key accelerator in data centers.

In the first work, we explore two secure memory architectures, counter-mode encryption and direct encryption, for GPUs, and show that we need to architect secure memory differently from it for CPUs. Our in-depth study reveals the following insights. First, as GPUs are designed for high-throughput computation, its secure memory needs to deliver high bandwidth. Second, with counter-mode encryption, the memory traffic resulting from the metadata, i.e., the counters, MACs (message-authentication codes), and integrity tree, may cause significant performance degradation, even in the presence of metadata caches. Third, the sectored cache structure adopted by GPUs leads to multiple sequential accesses to the same metadata cache line, which necessitates the use of MSHRs (miss-status handling registers) for meta-data caches. Fourth, unlike CPUs, separate/partitioned metadata caches perform better than unified metadata caches on GPUs. The reason is that GPU workloads feature streaming accesses, which cause severe contention in the unified metadata cache and the cached counters and integrity tree nodes may be evicted before being reused. Fifth, the massive-threaded nature of GPUs make them latency-tolerant and the performance impact due to the extra encryption/decryption latency is limited. As a result, direct encryption can be a promising alternative for GPU secure memory. The challenge, however, lies in memory integrity verification as the integrity tree may incur high storage overhead and metadata traffic.

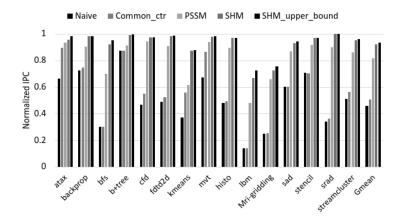

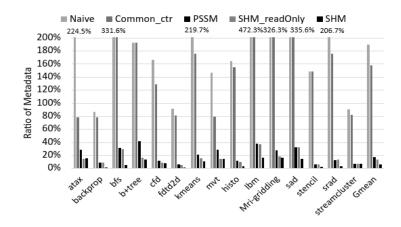

In the second work, we point out that conventional CPU secure memory architecture can not be directly adopted to the GPUs. The key reasons include: (1) accessing the security metadata, including encryption counters, message authentication codes (MACs) and integrity trees, requires significant memory bandwidth, which may lead to severe bandwidth competition with normal data accesses and degrade the GPU performance; (2) contemporary GPUs use partitioned memory organization, which results in storage and coherence problems for encryption counters and integrity trees since different partitions may need to update the same counter/integrity tree blocks; and (3) the existing split-counter block organization is not friendly to sectored caches, which are commonly used in GPU for bandwidth savings. Based on these observations, we propose partitioned and sectored security metadata (PSSM), which has two components: (a) using the offset addresses (referred to as local addresses) within each partition, instead of the virtual or physical addresses, to generate the metadata so as to solve the counter or integrity tree storage and coherence problems and (b) reorganizing the security metadata to make them friendly to the sectored cache structure so as to reduce the memory bandwidth consumption of metadata accesses. With these proposed schemes, the performance overhead of secure GPU memory is reduced from 59.22% to 16.84% on average. If only memory encryption is required, the performance overhead is reduced from 29.53% to 5.18%.

In the third work, we analyze the security guarantees that used to defend against physical attacks, and make the observation that heterogeneous GPU memory system may not always need all the security mechanisms to achieve the security guarantees. Based on the memory types as well as memory access patterns either explicitly specified in the GPU programming model or implicitly detected at run time, we propose adaptive security memory support for heterogeneous memory on GPUs. Specifically, we first identify the read-only data and propose to only use MAC (Message Authentication Code) to protect their integrity. By eliminating the freshness checks on read-only data, we can use a single counter for such data regions and remove the corresponding part in the Bonsai Merkel Tree (BMT), thereby reducing the traffic due to counters and BMT. Second, we detect the common streaming data access patterns and propose coarse-grain MACs for such stream data to reduce the MAC access bandwidth. With the hardware-based detection of memory type (read-only or not) and memory access patterns (streaming or not), our proposed approach adapts the security support to significantly reduce the performance overhead. Our evaluation using both memory-intensive and computation-intensive workloads shows that our scheme can achieve secure memory on GPUs with low overheads for memory-intensive workloads while not affecting computation-intensive workloads. Among the fourteen memory-intensive workloads in our evaluation, our design reduces the performance overheads of secure GPU memory from 53.9% to 10.2% on average. Compared to the state-of-the-art secure memory designs for GPUs [Na21; Yua21a], our scheme outperforms PSSM by up to 36.8% and 10.4% on average and outperforms Common counters by 77.5% on average for memory-intensive workloads.

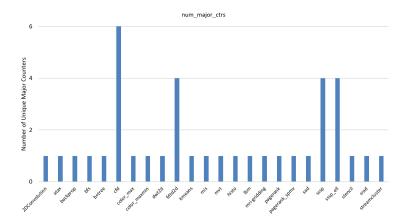

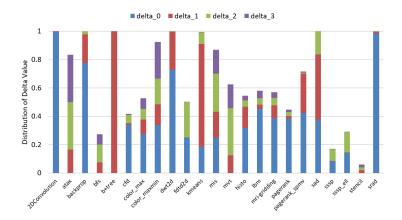

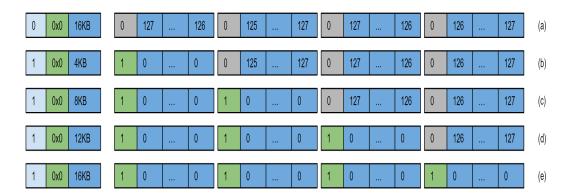

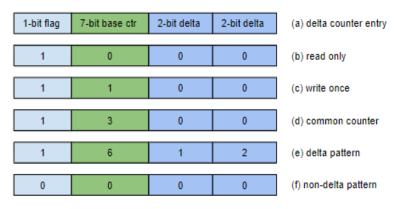

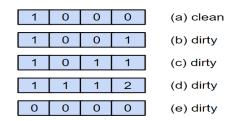

In the fourth work, we focus on encryption counters given their impact on the counter and BMT traffic while leveraging prior schemes [Sai18; Taa18a] to address the MAC traffic. We first analyze the characteristics of the encryption counters from a wide range of GPGPU benchmarks and make two key observations. (1) With the split counter scheme, the cache

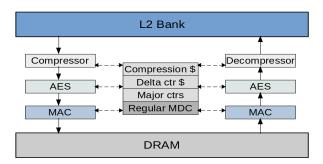

blocks in a large portion of the memory space, sometimes the entire GPU memory space, share the same major counter value. (2) The difference among minor counters is fairly limited. We then propose a novel scheme to reduce the encryption counter traffic. Our design includes (a) a highly compact way of counter representation and (b) a verification scheme to determine the correct minor counter values. In our design, we use a few on-chip registers to hold the major counters and use a (7-bit) base value along with two small (2-bit) deltas to represent the minor counters in a large memory chunk, one delta for the most frequent delta between minor counters and the base, the other delta for the maximal difference between a minor counter and the base. This way, for a large memory chunk (e.g., 16kB), the counter overhead becomes nearly negligible (less than 2B). We then leverage the existing MAC verification logic to verify the minor counters computed from the base and deltas. Our approach essentially trades off decryption and integrity-check latency for reduced counter-data traffic to take advantage of the latency-hiding nature of GPUs. Compared to prior works on reducing counter traffic [Na21], our scheme handles more counter value patterns (as we don't restrict the counters to be the same in a memory chunk) and is more effective in reducing counter traffic. Our study also reveals that the GPU memory data are typically compressible. As a result, we can co-locate the MACs with the compressed cache blocks, similar to [Taa18a]. Our experimental results show that our proposed delta counter scheme significantly reduces the storage and bandwidth overheads of encryption counters and achieves secure GPU memory with an average performance overhead of 2.01% compared to GPU without security support. Our delta scheme is also compatible with SYNERGY [Sai18], which leverages ECC chips to store MACs, and our achieved performance overhead is 2.83%.

© Copyright 2023 by Shougang Yuan

All Rights Reserved

#### Bandwidth-Efficient Secure Memory Designs for GPUs

by Shougang Yuan

#### A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

**Computer Engineering**

Raleigh, North Carolina 2023

APPROVED BY:

Dr. James Tuck

Dr. Xu Liu

Dr. Amro Awad

Dr. Huiyang Zhou Chair of Advisory Committee

## BIOGRAPHY

The author received his bachelor's degree of Information Management and Information System from Northwest A&F University in 2015, and his master's degree of Computer Science from Xi'an Jiaotong University in 2018. He started his Ph.D. program in North Carolina State University in 2018. His research mainly focused on secure memory architectures for non-volatile memory and GPU memory.

## ACKNOWLEDGEMENTS

I would like to express my gratitude to Dr. Huiyang Zhou, Dr. Amro Awad, Dr. James Tuck, and Dr. Xu Liu for serving on my committee, and thank Dr. Yan Solihin for his help and guidance during my PhD study.

## **TABLE OF CONTENTS**

| List of T | ables .                 |                                                                 | vii     |  |

|-----------|-------------------------|-----------------------------------------------------------------|---------|--|

| List of F | igures                  |                                                                 | viii    |  |

| Chapte    | r 1 IN                  | TRODUCTION AND BACKGROUNDS                                      | 1       |  |

| 1.1       |                         | uctions                                                         | 1       |  |

| 1.2       |                         | round                                                           | 2       |  |

|           | 1.2.1                   | Threat Model and Scope of Work                                  | 2       |  |

|           | 1.2.2                   | Security Mechanisms                                             | 3       |  |

| 1.3       |                         | ecurity                                                         | 5       |  |

| Chapter   |                         | nalyzing Secure Memory Architecture for GPUs                    | 6       |  |

| 2.1       |                         |                                                                 | 6       |  |

| 2.1       |                         |                                                                 | 8       |  |

| 2.2       |                         | odologyendology                                                 | 0<br>10 |  |

| 2.5       |                         | • •                                                             |         |  |

|           | 2.3.1                   | Performance Overhead                                            | 10      |  |

|           | 2.3.2                   | MSHRs for Metadata Caches                                       | 13      |  |

|           | 2.3.3                   | Metadata Cache Size                                             | 14      |  |

|           | 2.3.4                   | Unified vs. Separate Metadata Caches                            | 16      |  |

|           | 2.3.5                   | AES Engine Throughput                                           | 18      |  |

|           | 2.3.6                   | Die Area                                                        | 19      |  |

| 2.4       |                         | Encryption                                                      | 22      |  |

|           | 2.4.1                   | Performance Overheads of Direction Encryption                   | 22      |  |

|           | 2.4.2                   | Direct Encryption <b>vs.</b> Counter-mode Encryption            | 24      |  |

|           | 2.4.3                   | Integrity Protection                                            | 24      |  |

| 2.5       | Conclu                  | usions                                                          | 26      |  |

| Chapter   | r 3 PS                  | SSM: Achieving Secure Memory for GPUs with Partitioned and Sec- |         |  |

|           | to                      | red Security Metadata                                           | 27      |  |

| 3.1       | Motiva                  | ations                                                          | 27      |  |

|           | 3.1.1                   | Performance Impacts of Naive Design                             | 27      |  |

|           | 3.1.2                   | Problem Diagnosis                                               | 29      |  |

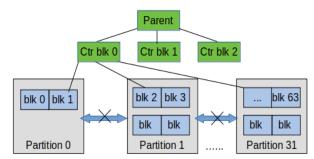

|           | 3.1.3                   | Coarse-Grain Interleaving                                       | 30      |  |

|           | 3.1.4                   | Sectored MDC                                                    | 31      |  |

|           | 3.1.5                   | Sectored Data Cache and MAC Verification                        | 33      |  |

| 3.2       | 3.2 Architecture Design |                                                                 |         |  |

|           | 3.2.1                   | Overall Architecture                                            | 35      |  |

|           | 3.2.2                   | Using Local Addresses for Security Metadata                     | 36      |  |

|           | 3.2.3                   | Making Metadata Friendly to Sectored Caches                     | 37      |  |

|           | 3.2.4                   | Encryption and MAC Engine                                       | 39      |  |

|           | 3.2.5                   | Bandwidth for Accessing MACs                                    | 40      |  |

| 3.3        | Evalua | ation                                                            | 41        |

|------------|--------|------------------------------------------------------------------|-----------|

|            | 3.3.1  | Methodology                                                      | 41        |

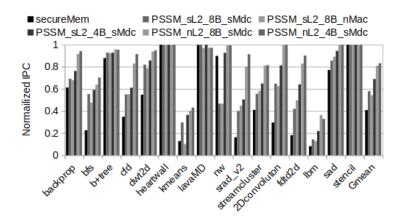

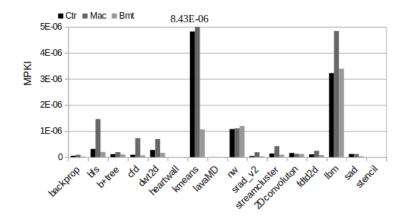

|            | 3.3.2  | Performance                                                      | 42        |

| 3.4        | Conclu | usions                                                           | 47        |

|            |        |                                                                  |           |

| Chapte     |        | HM: Adaptive Security Support for Heterogeneous Memory on GPUs   | <b>48</b> |

| 4.1        |        | ation and Design Principles                                      | 48        |

|            | 4.1.1  | Heterogeneous Memory on GPUs                                     | 48        |

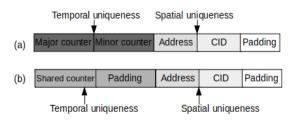

|            | 4.1.2  | Seed Generation in Counter-Mode Encryption                       | 49        |

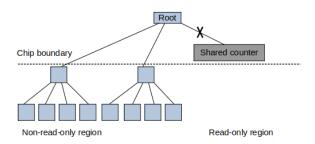

|            | 4.1.3  | Overhead of MAC Accesses                                         | 51        |

| 4.2        | Archit | ecture Design                                                    | 51        |

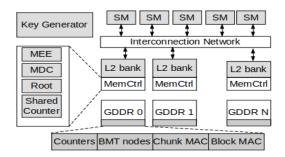

|            | 4.2.1  | Overall Architecture                                             | 51        |

|            | 4.2.2  | Detecting Read-only Regions                                      | 53        |

|            | 4.2.3  | Detecting Streaming Accessed Chunks                              | 56        |

|            | 4.2.4  | Using L2 as Victim Cache for Security Metadata                   | 59        |

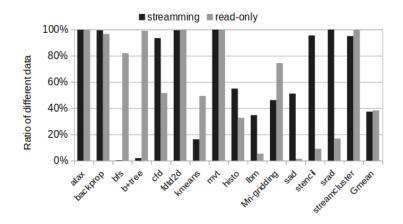

| 4.3        | Metho  | odology                                                          | 60        |

|            | 4.3.1  | Hardware Overheads                                               | 63        |

| 4.4        | Evalua | ation                                                            | 63        |

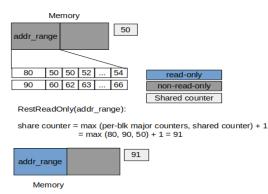

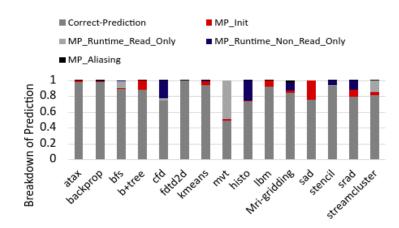

|            | 4.4.1  | Read Only Prediction                                             | 63        |

|            | 4.4.2  | Streaming Access Pattern Detection                               | 64        |

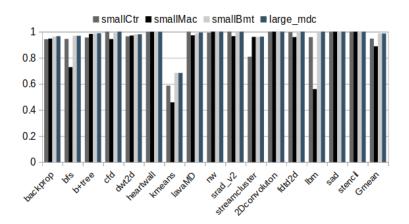

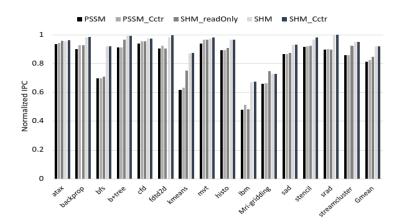

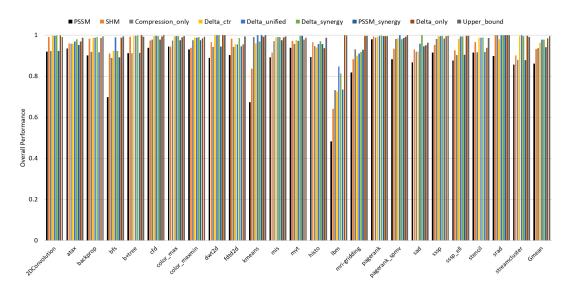

|            | 4.4.3  | Overall Performance                                              | 65        |

|            | 4.4.4  | Performance Breakdown                                            | 66        |

|            | 4.4.5  | Bandwidth Saving                                                 | 67        |

|            | 4.4.6  | Power Saving                                                     | 69        |

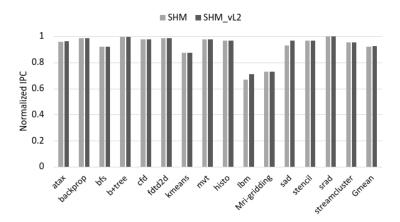

|            | 4.4.7  | Using L2 as a Victim Cache                                       | 69        |

| 4.5        | Conclu | usions                                                           | 70        |

|            |        |                                                                  |           |

| Chapte     |        | elta Counter: Bandwidth-Efficient Encryption Counter Representa- | - 1       |

| <b>F</b> 1 |        | on for Secure GPU Memory                                         | 71        |

| 5.1        |        | nary                                                             | 71        |

| 5.2        |        | ations                                                           | 72        |

|            |        | Major Counter Analysis                                           | 73        |

|            | 5.2.2  | Minor Counter Analysis                                           | 74        |

| - 0        | 5.2.3  | MAC Bandwidth Requirement                                        | 76        |

| 5.3        |        | ecture Design                                                    | 77        |

|            | 5.3.1  | Overall Architecture                                             | 77        |

|            | 5.3.2  | Management of Major Counter Registers                            | 77        |

|            | 5.3.3  | Delta Counter Entry                                              | 81        |

|            | 5.3.4  | Dataflow of DRAM Read and Write                                  | 82        |

|            | 5.3.5  | Delta Counter Cache Management                                   | 82        |

|            | 5.3.6  | Counter Cache and BMT Verification                               | 83        |

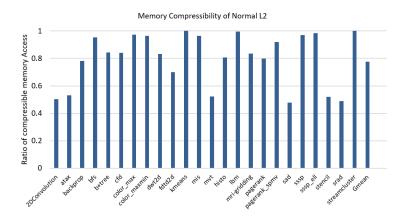

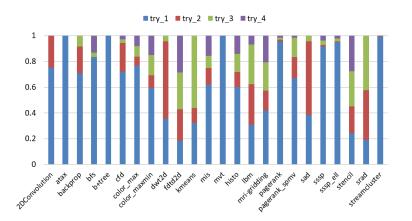

|            | 5.3.7  | Data Compressibility                                             | 84        |

| 5.4        | Metho  | odology                                                          | 86        |

| 5.5    | Evalua | ution                       | 88 |

|--------|--------|-----------------------------|----|

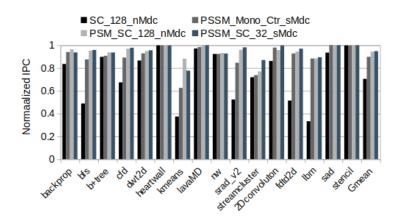

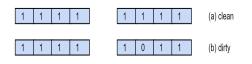

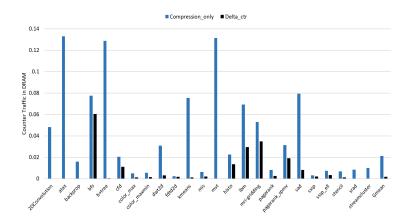

|        | 5.5.1  | Overall Performance         | 88 |

|        | 5.5.2  | Performance breakdown       | 88 |

|        | 5.5.3  | Upper Bound Analysis        | 92 |

| 5.6    | Conclu | usions                      | 92 |

| Chapte | r6 C0  | ONCLUSIONS AND FUTURE WORKS | 94 |

## **LIST OF TABLES**

| Table 2.1 | Baseline GPU configuration                                       | 8  |

|-----------|------------------------------------------------------------------|----|

| Table 2.2 | Metadata organization and storage                                | 9  |

| Table 2.3 | Metadata cache organization                                      | 9  |

| Table 2.4 | Benchmarks                                                       | 10 |

| Table 2.5 | Evaluated designs for counter-mode encryption                    | 11 |

| Table 2.6 | Die area of the AES engine                                       | 20 |

| Table 2.7 | Scaled down die area of the AES engine and caches                | 20 |

| Table 2.8 | Evaluated designs for direct encryption                          | 22 |

| Table 3.1 | Baseline GPU Configuration                                       | 41 |

| Table 3.2 | MDC and MEE Organization                                         | 41 |

| Table 3.3 | Benchmarks                                                       | 42 |

| Table 3.4 | Evaluated designs for GPU secure memory with both memory encryp- |    |

|           | tion and integrity verification.                                 | 43 |

| Table 3.5 | Evaluated designs for GPU memory encryption                      | 43 |

| Table 4.1 | Security Mechanisms for GPU Heterogeneous Memory                 | 49 |

| Table 4.2 | Security Mechanisms for Application Data                         | 49 |

| Table 4.3 | Handling Streaming Predictions for Read Accesses                 | 59 |

| Table 4.4 | Handling Streaming Predictions for Write Accesses                | 60 |

| Table 4.5 | Baseline GPU Configuration                                       | 61 |

| Table 4.6 | MDC and MEE Organization                                         | 61 |

| Table 4.7 | Benchmarks                                                       | 61 |

| Table 4.8 | Evaluated designs for GPU secure memory with both memory encryp- |    |

|           | tion and integrity verification.                                 | 62 |

| Table 4.9 | Hardware Overhead                                                | 63 |

| Table 5.1 | Baseline GPU Configuration                                       | 86 |

| Table 5.2 | MDC and MEE Organization                                         | 87 |

| Table 5.3 | Benchmarks                                                       | 87 |

| Table 5.4 | Evaluated designs for GPU secure memory with both memory encryp- |    |

|           | tion and integrity verification.                                 | 89 |

|           |                                                                  |    |

## **LIST OF FIGURES**

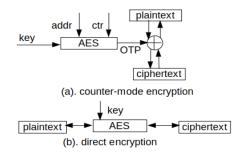

| Figure 1.1  | Counter-mode encryption and direct encryption                                | 3  |

|-------------|------------------------------------------------------------------------------|----|

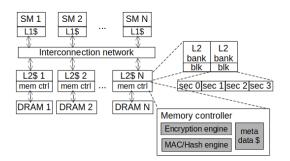

| Figure 2.1  | GPU architecture with secure memory support                                  | 7  |

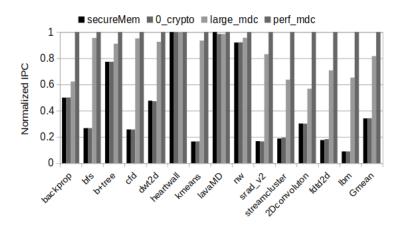

| Figure 2.2  | Normalized IPC of counter mode encryption with Bonsai Merkle tree.           | 12 |

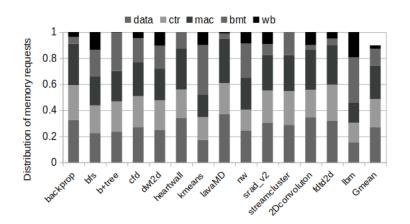

| Figure 2.3  | Distribution of different types of memory requests                           | 13 |

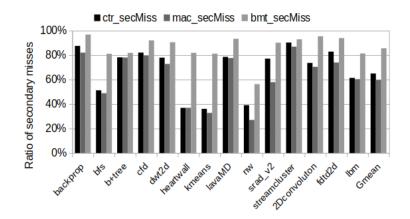

| Figure 2.4  | Amount of secondary misses in metadata caches                                | 14 |

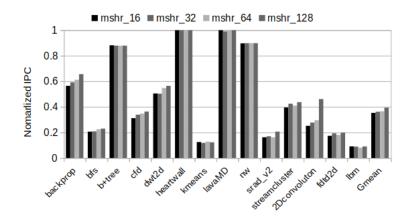

| Figure 2.5  | Normalized IPC of secure memory with different numbers of MSHRs              |    |

|             | in metadata caches                                                           | 15 |

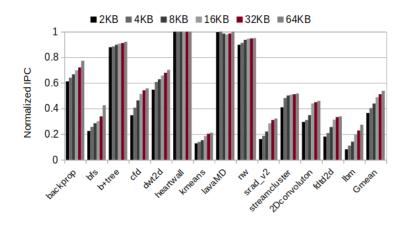

| Figure 2.6  | Normalized IPC for different metadata cache sizes                            | 15 |

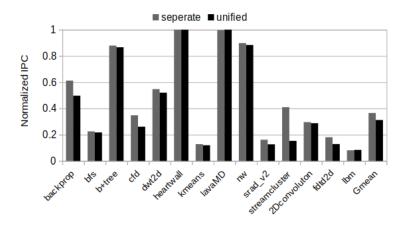

| Figure 2.7  | Normalized IPC of unified metadata caches vs separate metadata               |    |

| -           | caches.                                                                      | 17 |

| Figure 2.8  | Miss rates for different types of metadata in unified vs. separate meta-     |    |

|             | data caches.                                                                 | 17 |

| Figure 2.9  | Reuse distance of counters of the benchmark fdtd2d                           | 18 |

| Figure 2.10 | Reuse distance of MACs of the benchmark fdtd2d                               | 18 |

| Figure 2.11 | Normalized IPC with different numbers of AES engines in each mem-            |    |

|             | ory partition                                                                | 19 |

| Figure 2.12 | Normalized IPC with different L2 cache capacities                            | 21 |

| Figure 2.13 | L2 cache miss rate                                                           | 21 |

| Figure 2.14 | Normalized IPC of direct encryption with different encryption latencies.     | 22 |

| Figure 2.15 | Normalized IPC of direct encryption and counter-mode encryption              | 23 |

| Figure 2.16 | Normalized IPC of direct encryption and counter-mode encryption              |    |

|             | with integrity protection                                                    | 25 |

| Figure 3.1  | Normalized performance of secure memory designs to the baseline              |    |

|             | GPU without secure memory support                                            | 28 |

| Figure 3.2  | A single (128B) counter block corresponds to 128 data blocks in 32           |    |

|             | partitions. Similarly, one BMT node requires multiple counter blocks.        | 29 |

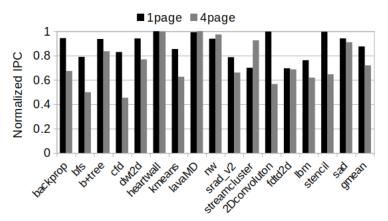

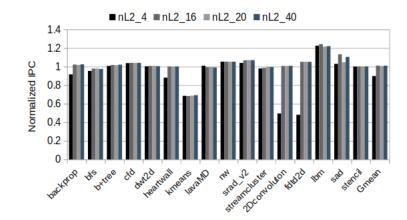

| Figure 3.3  | The IPC of different page interleaving granularities, normalized to          |    |

|             | the baseline GPU with 256B interleaving and without secure memory            |    |

|             | support                                                                      | 31 |

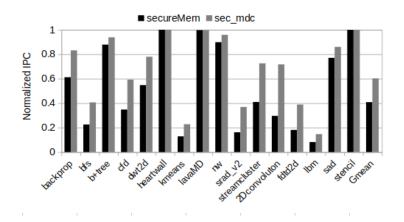

| Figure 3.4  | Performance comparison of secure GPU with non-sectored MDCs                  |    |

|             | (labeled 'secureMem') and sectored MDCs (labeled 'sec_mdc')                  | 32 |

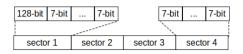

| Figure 3.5  | A Split-counter block of 128B, containing $1 \times 128$ -bit major counter  |    |

|             | and $128 \times 7$ -bit minor counters. When split into 4 sectors, the first |    |

|             | sector contains the major counter and some minor counters                    | 33 |

| Figure 3.6  | The IPC of a non-sectored L2 cache with different numbers of request         |    |

|             | merges in an L2 MSHR normalized to the baseline sectored L2                  | 34 |

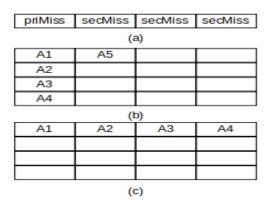

| Figure 3.7  | The L2 MSHRs. (a) The structure of an L2 MSHR. (b) The MSHR state            |    |

|             | of a sectored L2 after the access sequence A1-A5. (c) The MSHR state         |    |

|             | of a non-sectored L2 cache after the same access sequence A1-A5              | 35 |

| Figure 3.8  | Secure GPU architecture with the trust boundary as the GPU chip              | 36       |

|-------------|------------------------------------------------------------------------------|----------|

| Figure 3.9  | Physical and local addresses in partitioned memory organization              | 37       |

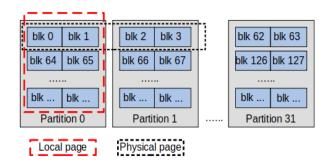

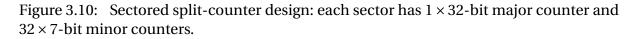

| Figure 3.10 | Sectored split-counter design: each sector has 1×32-bit major counter        |          |

|             | and 32 × 7-bit minor counters                                                | 38       |

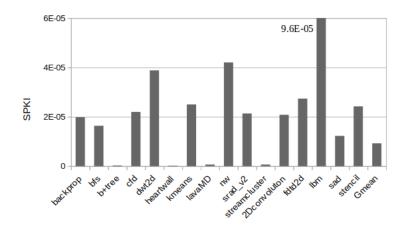

| Figure 3.11 | Numbers of stores per kilo instructions (SPKI)                               | 38       |

| Figure 3.12 | The encryption/decryption process in PSSM. The input to the AES              |          |

|             | encryption engine ensures encryption seed uniqueness, both tempo-            |          |

|             | rally and spatially.                                                         | 39       |

| Figure 3.13 | The MAC generation process in PSSM. The MAC computation output               |          |

|             | is truncated to 64/32 bits. Sector id is used when a MAC is generated        |          |

|             | for each sector.                                                             | 40       |

| Figure 3.14 | Normalized IPC of different secure GPU memory designs                        | 44       |

| Figure 3.15 | MDC miss rates (in MPKI) of the PSSM_nL2_4B_sMdc design                      | 45       |

| Figure 3.16 | Normalized IPC of the PSSM_nL2_4B_sMdc design with different                 |          |

|             | ideal MDCs                                                                   | 46       |

| Figure 3.17 | Normalized IPC of different GPU memory encryption schemes                    | 46       |

| Figure 4.1  | Seed generation for (a) not-read-only data and (b) read-only data            | 49       |

| Figure 4.2  | Integrity tree with read-only regions excluded.                              | 50       |

| Figure 4.3  | The ratio of memory accesses (i.e., L2 misses and L2 write backs)            |          |

|             | accessing streaming data as well as read-only data in various GPU            |          |

|             | workloads.                                                                   | 52       |

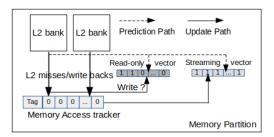

| Figure 4.4  | Overall architecture.                                                        | 53       |

| Figure 4.5  | The read-only detector and streaming detector in a memory partition.         |          |

|             | Their inputs are the LLC misses and write backs                              | 56       |

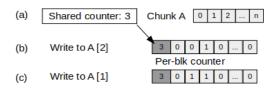

| Figure 4.6  | An example showing the propagation from the shared counter to the            |          |

| <b></b>     | per block counters.                                                          | 56       |

| Figure 4.7  | The process of shared counter update when using the read only reset          |          |

|             | API.                                                                         | 56       |

| Figure 4.8  | Breakdown of read-only predictions.                                          | 64       |

| Figure 4.9  | Breakdown of streaming pattern predictions                                   | 65       |

|             | Normalized IPC of different secure GPU memory designs                        | 66       |

| 0           | Performance impacts of different optimizations.                              | 67       |

| Figure 4.12 | Bandwidth overheads due to security metadata, normalized to regu-            | <u> </u> |

| Eigene 4 12 | lar data bandwidth, of different designs.                                    | 68<br>60 |

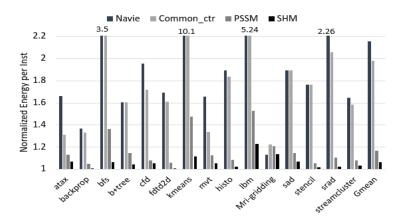

| U           | Normalized Energy Consumption per Instruction for different designs.         | 69       |

| Figure 4.14 | Normalized IPC when enabling L2 as a victim cache for security meta-<br>data | 70       |

|             |                                                                              | 70       |

| Figure 5.1  | Number of Unique Major Counters                                              | 73       |

| Figure 5.2  | Distribution of delta value that less than 4                                 | 75       |

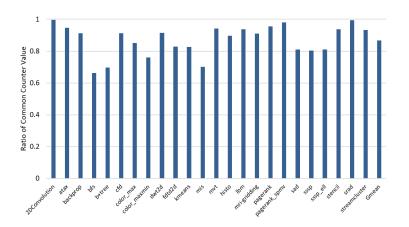

| Figure 5.3  | Average ratio of the most common counter value in a 16kB region of           |          |

|             | which the delta among minor counters is less than 4                          | 75       |

| Figure 5.4  | Data and MAC layout.                                          | 76 |

|-------------|---------------------------------------------------------------|----|

| Figure 5.5  | Overall architecture.                                         | 78 |

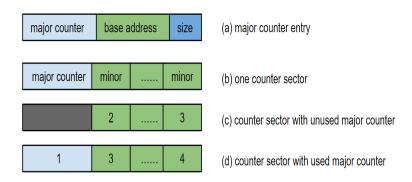

| Figure 5.6  | Major Counter Entry and Layout of Per-Block Counter.          | 79 |

| Figure 5.7  | An example of major counter register management               | 79 |

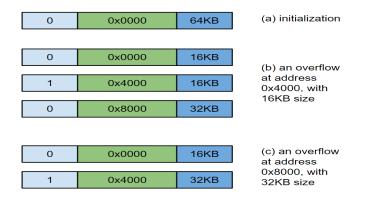

| Figure 5.8  | Handling of Minor Counter Overflow                            | 80 |

| Figure 5.9  | Delta counter representation and associated access patterns   | 81 |

| Figure 5.10 | DRAM flow for memory read and write.                          | 82 |

| Figure 5.11 | Delta Counter Management                                      | 83 |

| Figure 5.12 | Counter Cache Management                                      | 84 |

| Figure 5.13 | Compression Cache Management                                  | 85 |

| Figure 5.14 | Overall Performance of Different Designs                      | 90 |

| Figure 5.15 | Ratio of Counter Traffic in Memory.                           | 91 |

| Figure 5.16 | Ratio of Compressible Memory Access.                          | 91 |

| Figure 5.17 | Distribution of Number of Encryptions that Each Memory Access |    |

|             | Needs to Try                                                  | 92 |

|             |                                                               |    |

## CHAPTER

## INTRODUCTION AND BACKGROUNDS

## 1.1 Introductions

Cloud computing has become the predominant computing paradigm. With the cloud being a shared resource, it is critical to provide users with sufficient privacy and security guarantees. Toward this end, hardware-based trusted execution environments (TEEs), such as Intel SGX [Gue16b; Cor19] and ARM TrustZone [Pin19], have been integrated onto the CPUs to provide secure isolated computing environment for cloud users. TEEs can protect against both compromised system software, e.g., hypervisors and operating system (OS), and physical attacks such as memory tampering [Gue16b]. A critical building block for TEE is *secure memory engine*, which keeps data in memory encrypted [Gue16a; Kap16] and protects its integrity [Gue16a]. However, such secure memory architecture support is missing on GPUs, a key accelerator in clouds for a wide range of workloads including machine learning, scientific computing, 3D rendering, etc. As the system security is determined by its weakest link, we argue that accelerators such as GPUs also need to provide TEE.

Recognizing the needs, some recent works, including Graviton [Vol18] and HIX [Jan18],

tried to provide TEE for the workloads offloaded to GPUs. Graviton assumes that the system software stack, including GPU drivers, the OS, and hypervisor, cannot be trusted and the attackers have physical access to the hardware. To protect against software attacks, the GPU management operations are offloaded to the GPU command processors instead of being relegated to the GPU drivers, which runs within the untrusted host kernel space. Furthermore, Graviton provides new primitives, such as secure memory copy, to prevent attackers from snooping upon the PCIe bus. HIX, alternatively, mainly focuses on protecting the I/O path between the hardware and software. Although it also keeps the GPU drivers out of the trust boundary by isolating it from the kernel space, it relies on the secure CPU enclaves to protect the refactored GPU drivers. However, in these previous works, the threat model is weaker than conventional CPU TEE, as they do not provide secure memory support and require system software (e.g., GPU driver) to be trusted.

In this dissertation, we explore the design space and implication of supporting hardware based TEEs for GPUs. We start our investigation with a detailed performance analysis for GPU secure memory designs, and identified that the memory bandwidth competition between the regular data and security metadata is the major performance bottleneck. In our second work, we propose a simple yet effective scheme, called PSSM (Partitioned and Sectored Security Metadata), to alleviate the memory bandwidth pressure of security metadata access. In our third work, we analyze the different security mechanisms in conventional CPU TEEs, and argue that heterogeneous GPU memory may not always need all the security guarantees as conventional CPU TEEs. And in our last work, we analyze the encryption counter behaviors, and propose an bandwidth efficient encryption counter representation, namely, delta counter, for secure GPU memory.

## 1.2 Background

#### 1.2.1 Threat Model and Scope of Work

The threat model for CPU TEE, such as Intel SGX, assumes two types of threats: compromised system/privileged software (such as the OS and hypervisor) and attackers that have physical access to the remote server and the abilities to snoop/scan and modify data stored in off-chip memory. CPU TEE assumes that the processor chip provides a security boundary, where all on-chip components are assumed to be out of the reach of attackers. In general, TEE requires three major architecture supports: *hardware key management, attestation*, and *secure memory engine* (which encrypts and protects the integrity of data stored off the processor chip) [Lie00; Suh07; Yan03; Yan06]. Of these, secure memory incurs the largest performance overheads as it must be active at all time and affects the critical path of load instructions. Due to the enormity of the overheads, recent attempts to extend CPU TEE to GPUs [Jan18; Vol18] ignore the physical attack threats and enlarge the trust base (e.g., adding GPU memory module to the trust base). In contrast, this research assumes the same threat model in CPU TEE also affects GPUs, and assumes that GPU chip provides the security boundary, where all the data stored in the on-chip resources such as registers and caches are safe. The attackers may have physical access to the GPUs hardware, and have the capability to snoop the GPU memory buses or to scan/tamper the GPU memory content.

The scope of this paper covers the design space of secure memory for GPUs. Hardware key management and attestation have been well studied in previous work (i.e., Graviton [Vol18] and HIX [Jan18]) and are beyond the scope of this paper. Securing the communication channel between CPU and GPU is also outside the scope of this work. Existing solutions for that may include PCI modification [Jan18], or for tighter integration, secure cache coherence protocol [Rog08a]. Furthermore, side channel attacks such as timing-based side channel attack [Jia16] are also out of the scope of our work.

#### 1.2.2 Security Mechanisms

**Memory encryption.** The goal of memory encryption is to protect data confidentiality [Lee05; Rog08b; Rog06; Zha05]. The cryptographic hardware engines residing in the memory controller are responsible for performing encryption/decryption before the data is sent to/returned from the off-chip memory. Generally, there are two approaches for memory encryption as shown in Fig. 1.1: counter-mode encryption and direct encryption.

Figure 1.1: Counter-mode encryption and direct encryption

Counter-mode encryption can hide the decryption latency by overlapping it with memory reads, and thus offload the decryption latency from the critical path of load instructions. In counter-mode encryption, there is a counter associated with each cache line. When the memory controller is fetching the data from off-chip memory, the corresponding counter and the block address are used to generate a one-time pad (OTP) using the encryption engine such as AES. The memory controller can recover the plaintext by XORing the data and OTP in one cycle and then supply the data to processors. To guarantee the security, the counters cannot be reused. Hence, at each dirty eviction from the last level cache (LLC), the counter corresponding to the cache line will be incremented. Since the encryption strength of counter-mode memory encryption is conditional upon not reusing the counters, if the attacker can trigger reuse of counters, the encryption will be broken [Yan06; Rog07]. Therefore, counter-mode encryption *fundamentally relies* on counter integrity protection to provide data confidentiality.

Direct encryption can also be used for the security purpose. In contrast to counter-mode encryption, with direct encryption, confidentiality does not necessarily require integrity protection. The main disadvantage of direct encryption is that it exposes the latency of decryption to the critical path of memory reads, because decryption can only start after the data is fetched from memory [Suh03].

**Memory Integrity Verification.** As discussed earlier, counter-mode encryption requires integrity protection of counters [Rog07]. Furthermore, MACs are needed to protect against memory tampering attack [Yan06; Zou19]. As pointed out by Rogers et. al [Rog07], stateful MACs calculated from the ciphertext, block address and the corresponding counter can provide data integrity protection, and the Merkle tree (MT) only needs to cover the counters to protect against counter-replay attacks. This scheme is named BMT and can help to reduce the storage overheads of the MT. Moreover, the BMT is much shallower than the original MT. Any modification to the data or MACs stored in the off-chip memory can be detected by comparing the MACs when the data is fetched from memory. Similarly, any modification or replay of the counters can be detected by traversing the BMT and comparing the hash values in the BMT nodes. In contrast, with direct encryption, encryption protection is not dependent on integrity verification; and integrity verification provides additional protection against memory tampering and replay attacks. Integrity protection relies on (1) MAC of the ciphertext and (2) a Merkle/Hash Tree based on the entire memory with a special on-chip register storing the root of the tree [Gas03].

## 1.3 GPU Security

Recent studies highlight the needs for security support within accelerators. Deep learning (DL) is such an application that attracts special attention [Liu17]. Several recent works [Zuo20; Hua20b; Hua20a] aim to extend the existing memory encryption and integrity verification schemes to DL accelerators.

The work [Zuo20] by Zuo et al. pointed out that the gap between the throughput of AES engine and the GPU memory bandwidth is the key bottleneck for secure GPU memory. To reduce the overhead of encryption, they proposed: (1) selective memory encryption, (2) co-location of data and the corresponding counter. In comparison, our work differs from this prior work in the following ways. First, our work consider data integrity protection, which is missing in this prior work. Second, we perform a detailed study on metadata cache designs, including the impact from the sectored L2 caches as well as unified metadata caches and separate metadata caches. Third, we exploit pipelined AES engines to overcome the AES throughput limitation and explore the design trade-offs for different AES throughput. Fourth, the proposed solution by Zuo et al. [Zuo20] is specific to DL while our work covers a wide range of workloads.

Similar to Zuo's work [Zuo20], Hua et al. [Hua20b; Hua20a] aimed to provide memory protection for the deep learning workloads running on the accelerators. As mentioned in [Hua20b], the overheads of memory encryption and integrity verification come from the extra memory accesses generated by the security metadata. In their system design, they proposed to provide memory encryption and integrity verification based on a coarse granularity of memory objects. Their key observation is that accelerators often explicitly move data between on-chip memory and off-chip DRAM at the object granularity. In comparison, our work provides detailed performance analysis of both counter-mode encryption and direct encryption and explore different metadata cache design choices.

Other works, including HIX [Jan18] and Graviton [Vol18] that aimed to provide the TEE for GPUs, mainly focused on protecting the user program and data from untrusted OS or privileged malicious software (hypervisor), and did not consider the physical attacks, i.e., memory scanning and tampering attacks. In other words, these two works did not provide hardware-based memory encryption and integrity verification protections. The data stored on GPU off-chip memory is plaintext and there is no support for integrity checks. In comparison, our work defines a stronger threat model, and provides detailed performance study on memory encryption and integrity verification for GPUs.

## CHAPTER

2

# ANALYZING SECURE MEMORY ARCHITECTURE FOR GPUS

## 2.1 Introduction

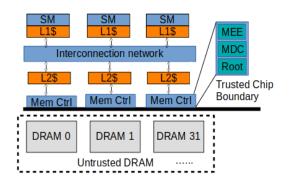

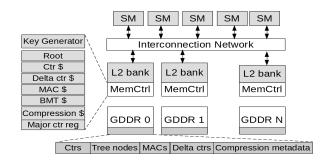

Similar to the CPU TEE (e.g., Intel SGX), the secure memory hardware is placed in the memory controller in our design, as shown in Fig. 2.1. As GPUs incorporate multiple memory controllers to provide high memory bandwidth, the same secure memory hardware is replicated in each memory controller.

We start our investigation with counter-mode encryption and Bonsai Merkle Tree (BMT) [Rog07], which are the state-of-art secure memory architecture on CPUs. Counter-mode encryption is introduced to hide the decryption latency and BMT is used to verify the integrity of data through its counters, which are used to encrypt/decrypt the data along with the secret key. In counter-mode encryption, the security metadata include counters, BMT, and MACs of the ciphertext. To reduce the extra memory accesses for fetching the metadata, on-chip metadata caches are commonly employed. We model the counter-mode encryption and BMT support upon a GPU model based on Nvidia Volta [Jia18]

architecture, and identify that hardware-based secure memory architecture can incur significant performance overhead for GPUs. The main reason is that the metadata data accesses generate a lot of memory traffic even in the presence of metadata caches. Given the high bandwidth requirements of GPUs, the additional memory traffic contends for the memory bandwidth and significantly slows down the GPUs performance. Also, we observe that due to the sectored L2 cache structure in GPUs, the streaming data accesses leads to a high ratio of secondary misses (i.e., misses to the same cache block after it being requested) in the metadata caches, which highlight the importance of the MSHRs to filter out redundant memory requests. Furthermore, due to the nature of high-throughput computation of GPUs, high-throughput cryptographic engines are also needed to produce a balanced system.

Besides counter-mode encryption, we also analyze the alternative design of direct encryption. Without counters, BMT is infeasible. Therefore, we resort to a Merkle Tree (MT) to perform integrity checks. In other words, with direct encryption, the security metadata include MACs and the MT, both of them are used for memory integrity verification. Our analysis reveals the following interesting observations. First, direct encryption itself does not lead to high performance overheads because GPUs are designed to be latency tolerant. Actually, our results show that direct encryption can perform better than counter-mode encryption even with a high encryption latency of 160 cycles. Second, memory integrity protection may become the performance bottleneck due to the memory traffic generated by MAC and MT accesses.

Figure 2.1: GPU architecture with secure memory support

| SM config     | 80 SMs, 1132 MHz                  |  |

|---------------|-----------------------------------|--|

| Register File | 256KB/SM, 20MB in total           |  |

| L1 D-Cache    | 32KB/SM                           |  |

| Shared Memory | 96KB/SM                           |  |

| L2 cache      | 2 banks/partition, 96KB/bank, 6MB |  |

|               | in total                          |  |

| DRAM          | 850MHz, 868GB/s, 32 partitions    |  |

Table 2.1: Baseline GPU configuration

## 2.2 Methodology

We model different secure memory architecture supports using GPGPU-Sim v4.0 [Kha20]. The configuration of our baseline GPU model is shown in Table 2.1, which is based on the Nvidia Volta architecture [Jia18]. In our experiments, we assume that a range of 4GB device memory is protected, and the metadata cache line size is aligned to the data cache line size, which is 128B. The metadata organization and storage overhead are listed in Table 2.2.

For counter-mode encryption, each counter cache line maintains one 128-bit major counter (shared by data blocks within a 16KB memory chunk) and 128 7-bit per block minor counters, thereby covering 128 lines of data. In other words, the ratio between data and counter capacity is 128 and the overall counter blocks take 32MB (=4GB/128) off-chip storage. Using a 64-bit MAC for each 128B data, the overall MAC consumes 256MB storage. As a result of the sectored L2 cache, we use truncated MAC, i.e., 16-bit MAC for each 32B sector. For the BMT, we build a 6-level 16-ary hash tree and its overall capacity is 2.14 MB, excluding the counter blocks that serve as the leaf nodes of the BMT. Therefore, the overall capacity of metadata is 290.14MB (=32+256+2.14 MB) for counter-mode encryption.

With direct encryption, using the same 64-bit MAC for each 128B data, the overall MAC consumes 256MB memory. As the MT is built upon the 4GB data, we use a 7-level 16-ary tree and the overall capacity is 17.1MB, excluding the MACs that serve as the leaf nodes of the MT. Therefore, the overall memory overhead is 273.1MB (=256+17.1 MB) for direct encryption.

The separate metadata caches, which include the counter cache, MAC cache, and BMT/MT cache, are modeled in each memory partition (i.e., each memory controller). The metadata cache specification is listed in Table 2.3. State-of-the-art secure memory architecture in CPUs uses speculative verification and lazy update for BMT/MT [Gas03]. We also adopt these schemes on GPUs. Speculative verification means that the memory

| Metadata Type | Counter-mode Encryp-<br>tion | Direct Encryption        |  |

|---------------|------------------------------|--------------------------|--|

| Counter       | 128b/16KB, 7b/blk,           | -                        |  |

|               | 32MB                         |                          |  |

| MAC           | 8B/blk, 2B/sector,           | 8B/blk, 2B/sector,       |  |

|               | 256MB                        | 256MB                    |  |

| BMT/MT        | 16 ary, 6 levels, 2.14MB     | 16 ary, 7 levels, 17.1MB |  |

Table 2.2: Metadata organization and storage

| Table 2.3: | Metadata | cache | organization |

|------------|----------|-------|--------------|

|------------|----------|-------|--------------|

| Counter cache          | {2,4,8,16,32,64}KB/Memory Partition, 2KB default,<br>128B blk, 64 MSHRs, allocate-on-fill policy |  |

|------------------------|--------------------------------------------------------------------------------------------------|--|

|                        | 128B blk, 64 MSHRs, allocate-on-fill policy                                                      |  |

| Mac cache              | {2,4,8,16,32,64}KB/Memory Partition, 2KB default,                                                |  |

|                        | {2,4,8,16,32,64}KB/Memory Partition, 2KB default, 128B blk, 64 MSHRs, allocate-on-fill policy    |  |

| (Bonsai)Merkle Tree    | {2,4,8,16,32,64}KB/Memory Partition, 2KB default,                                                |  |

| cache                  | {2,4,8,16,32,64}KB/Memory Partition, 2KB default, 128B blk, 64 MSHRs, allocate-on-fill policy    |  |

| Unified metadata cache | 6KB/Memory Partition, 128B blk, 192 MSHRs,                                                       |  |

|                        | allocate-on-fill policy                                                                          |  |

| Hash/Mac latency       | 40 cycles default                                                                                |  |

| AES engines            | {1,2}/Memory Partition, 2 default.                                                               |  |

controller can supply the data to the core before the corresponding integrity check is finished. Later on, if there is a failure in integrity verification, an exception would be raised. Lazy update means that only when a counter block or a tree node is evicted from the counter cache or BMT/MT cache, its parent will be updated in the BMT/MT cache.

In our study, we assume pipelined AES engines and pipelined MAC units. This way, the encryption latency or the MAC computation latency would not affect the throughput. With AES-128, 16B of data can come out of a pipelined AES engine each cycle. With the memory clock frequency of 850MHz, the throughput of the pipelined AES engine is 13.6 GB/s (=16B\*850MHz). With 2 AES engines in each memory partition, the throughput would match the memory bandwidth, resulting in a balanced design. Therefore, we use 2 pipelined AES engines in each partition by default. We model different AES latencies and a 40-cycle latency for the MAC unit. With counter-mode encryption, the AES latency does not matter as it is hidden by design.

Our benchmarks are selected from the Rodinia-3.1 [Che09], Parboil [Str09] and polybench [GG09] benchmark suites to cover a wide range of workloads. Table 2.4 lists the details of these benchmarks. For each benchmark, we simulate until it has run for 4 million cycles.

| Categorization      | Benchmark name | Bandwidth utilization | IPC      |

|---------------------|----------------|-----------------------|----------|

| non                 | heartwall      | <1%                   | 1,195.37 |

|                     | lavaMD         | <1%                   | 4,615.23 |

| memory<br>intensive | nw             | <2%                   | 23.90    |

| Intensive           | b+tree         | 12%-14%               | 2,768.61 |

| medium              | backprop       | 25%                   | 3,067.61 |

|                     | cfd            | 15%-50%               | 1,076.98 |

| memory<br>intensive | dwt2d          | 20%-50%               | 784.70   |

| Intensive           | kmeans         | 40%-45%               | 97.04    |

|                     | bfs            | 5%-60%                | 699.51   |

|                     | srad_v2        | 79%- 80%              | 3,306.82 |

| memory              | streamcluster  | 78%-80%               | 1,178.18 |

| intensive           | 2Dconvolution  | 53%                   | 2,487.22 |

|                     | fdtd2d         | 82%-83%               | 1,773.95 |

|                     | lbm            | 58%                   | 552.12   |

Table 2.4: Benchmarks

Table 2.4 also reports the bandwidth utilization and the IPC (instruction-per-cycle) for each benchmark when running on the baseline GPU without secure memory support. In this paper, we categorize the benchmarks which consume more than 50% peak DRAM bandwidth as memory intensive, the benchmarks which consume less than 20% peak DRAM bandwidth as non memory intensive, and the remaining as medium memory intensive.

## 2.3 Counter-Mode Encryption

In this section, we perform an in-depth study on extending counter-mode encryption and BMT to GPUs. Different design options, as listed in Table 2.5, are explored to reveal the performance bottlenecks.

## 2.3.1 Performance Overhead

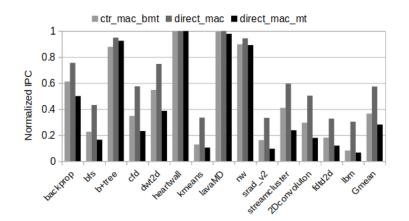

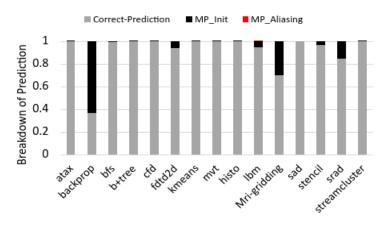

Fig. 2.2 shows the performance of various GPU secure memory models normalized to the baseline GPU without security support. From the figure, we can see that adding secure memory support may incur significant performance overhead. The normalized IPC is reduced by 65.9% on average using the geometric mean (Gmean), and can be up to 91.06% for memory-intensive workloads such as lbm.

To identify the performance bottleneck, we model different idealistic designs. From

| Scheme        | What It Represents                                  |  |

|---------------|-----------------------------------------------------|--|

| baseline      | Baseline GPU without secure memory support.         |  |

| secureMem     | Baseline GPU with secure memory support             |  |

|               | using counter-mode encryption and BMT. In           |  |

|               | Section 2.3.1, no MSHR is modeled, in Sec-          |  |

|               | tion 2.3.2, 2.3.3, 2.3.4, 2.3.5, there are 64 MSHRs |  |

|               | for each metadata cache.                            |  |

| secureMem_xMB | secure GPU memory with different L2 capacities      |  |

|               | upon our baseline GPU with counter-mode en-         |  |

|               | cryption and BMT.                                   |  |

| 0_crypto      | secureMem with 0 MAC latency and encryption         |  |

|               | latency.                                            |  |

| perf_mdc      | secureMem with perfect metadata caches, i.e.,       |  |

|               | there are no cache misses and write backs.          |  |

| large_mdc     | secureMem with unlimited capacity for metadata      |  |

|               | caches, meaning that there are only cold misses.    |  |

| mshr_x        | secureMem with different mshr capacity for meta-    |  |

|               | data caches.                                        |  |

| separate      | secureMem with separate metadata caches in each     |  |

|               | memory partition/unit.                              |  |

| unified       | secureMem with a unified metadata cache, which      |  |

|               | caches all types of metadata, in each memory par-   |  |

|               | tition/unit.                                        |  |

Table 2.5:Evaluated designs for counter-mode encryption

Fig. 2.2, we can see that zero cycle cryptographic operation latency (zero-cycle MAC and AES) does not alleviate the performance overhead. This is expected as GPUs are massively parallel machines and leverage high-degrees of TLP to hide the latency. However, when we model ideal metadata caches or unlimited capacity metadata caches, the GPU performance with secure memory support becomes very close to the baseline. This indicates that the accesses to the security metadata is the performance bottleneck.

Figure 2.2: Normalized IPC of counter mode encryption with Bonsai Merkle tree.

To further analyze the impact of the metadata accesses, in Fig. 2.3 we compare the amounts of different types of memory requests when secure memory is integrated, i.e., the secureMem model in Table 2.5. The memory-request types include regular data read and write requests (labeled 'data'), counter reads (labeled 'ctr'), MAC reads (labeled 'mac'), BMT reads (labeled 'bmt'), and all the writebacks from the metadata caches (labeled 'wb').

From Fig. 2.3, we can make the following observations. First, for all benchmarks, the memory requests to fetch MACs from off-chip memory account for a major portion of the memory traffic (25.58% on average). Second, the counter requests also account for a large portion of memory traffic (21.77% on average). Third, some benchmarks, including bfs, b+tree, kmeans, nw and lbm, have a relatively high ratio of memory requests for fetching the BMT blocks from memory. The reason is that these benchmarks have relatively high counter-cache miss rates and the fetched counters need to be validated. Fourth, extra memory traffic due to metadata accesses may not necessarily lead to performance degradation. For example, for the non-memory intensive benchmarks (heartwall, lavaMD and nw), the metadata accesses account for a large portion of the memory traffic (66.07%,

62.71%, 75.41%), but the performance impact is near zero. The reason is that for these benchmarks, the memory bandwidth is under-utilized as shown in Table 2.4. Therefore, additional traffic does not result in contention for the memory bandwidth. Fifth, some benchmarks, including bfs, dwt2d and lbm, have relatively high amounts of metadata-cache writebacks, which also impact the performance.

Figure 2.3: Distribution of different types of memory requests.

## 2.3.2 MSHRs for Metadata Caches

As shown in Fig. 2.3, metadata accesses are the main contributor for additional memory traffic. A deeper analysis reveals that many metadata cache misses are secondary misses, meaning that the missed metadata blocks have already been requested but have not returned from the memory. We report the ratio of secondary misses in different benchmarks in Fig. 2.4. We can see that the secondary misses account for 64.96%, 59.67% and 85.63% for counter/MAC/BMT cache misses on average. And it can be even more than 90% for some memory-intensive benchmarks like streamcluster. The reason is that contemporary GPUs usually employ the sectored cache structures to reduce memory bandwidth requirement. However, the sectored L2 cache combined with streaming data access pattern will lead to multiple sequential access to the same cache line in metadata cache. Suppose we have a streaming memory access pattern with 4 memory requests {0x0, 0x20, 0x40, x60}. In a non-sectored L2 cache with 128B cache line, one cache miss will be generated, which in turn leads to one counter/MAC cache miss. With a sectored L2 cache (4 sectors and each sector

size of 32B), in contrast, four L2 misses are generated, which leads to four counter/MAC cache misses (1 primary and 3 secondary) to the same counter/MAC cache line.

Figure 2.4: Amount of secondary misses in metadata caches.

The solution to avoiding the memory traffic generated by the secondary metadata cache misses is to add MSHRs to metadata caches. Here, we show the performance impact with different MSHR sizes for metadata caches and the results are shown in Fig. 2.5. Due to the metadata cache organization (i.e., one metadata cache line may cover multiple data cache lines/sectors), we assume each MSHR entry can merge at most 512/64/64 requests in the counter/MAC/BMT cache. As we can see from Fig. 2.5, 64 MSHRs in a metadata cache can be a good choice considering the performance and hardware cost. Hence, we assume 64 MSHRs as the default size in our experiments.

#### 2.3.3 Metadata Cache Size

In the next experiment, we vary the metadata cache size from 2KB to 64KB. The performance results are shown in Fig. 2.6. Since our baseline GPU has 32 memory partitions, the overall metadata cache capacity would vary from 192KB (=32x3x2KB) to 6MB (=32x3x64KB).

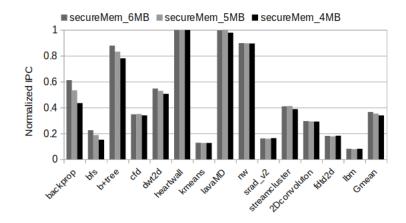

As expected, enlarging the metadata cache reduces the memory traffic and improves the performance. However, there is still a performance degradation of 46.17% on average even when the overall metadata cache capacity is enlarged to 6MB in total, which is equal to the capacity of our baseline GPU. For memory-intensive benchmarks, the performance overhead can be even more significant. For example, with the 6MB metadata cache, secure

Figure 2.5: Normalized IPC of secure memory with different numbers of MSHRs in metadata caches.

memory support still slows down the GPUs by 78.87% for kmeans, 67.82% for srad\_v2 and 72.64% for lbm. On one hand, these benchmarks have very high memory bandwidth utilization, therefore any additional memory traffic will incur more contention to the memory system. On the other hand, these benchmarks have many cold misses even in the presence of large metadata caches.

In the baseline GPU, each memory partition has 192KB (=92KB\*2) L2 cache capacity, and each counter cache line has 128 minor counters. To maintain the counters for all the L2 cache blocks in this memory partition, the capacity of counter cache should be at least 192KB/128 = 1.5KB. Therefore we use 2KB as the default size for metadata caches in each memory partition.

Figure 2.6: Normalized IPC for different metadata cache sizes.

#### 2.3.4 Unified vs. Separate Metadata Caches

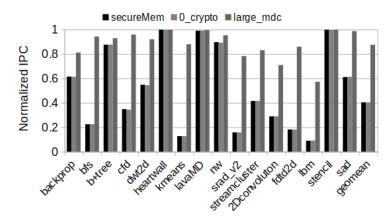

On CPU secure memory, Lehman et al.[Leh18] have studied the metadata cache access patterns and concluded that caching all metadata together in an unified metadata cache is better than caching them in separate metadata caches. In our experiment, we model an unified metadata cache in each memory partition that has the same capacity as the combined capacity of the three separate metadata caches. The performance comparison between the unified and separate metadata caches is shown in Fig. 2.7.

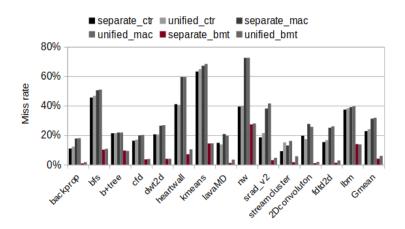

From Fig. 2.7 we can see that in contrast to CPUs, separate metadata caches outperform the unified metadata cache on GPUs. To figure out the reason, we report the miss rates of different types of metadata in Fig. 2.8. From Fig. 2.8, we can see that with unified metadata cache, the miss rate of different metadata all raises. From 22.77% to 24.03% for encryption counters, from 31.75% to 31.82% for MACs and from 4.02% to 5.93% for BMT. The reason is, the newly fetched metadata blocks keep on evicting the other metadata blocks from the unified metadata cache due to the streaming access pattern of the GPU workloads, which results in higher metadata misses. Moreover, every evicted counter and BMT node may need to update their parents, which potentially leads to more write updates to the BMT cache and more dirty evictions from BMT nodes. Our evaluation results show that the memory traffic due to metadata writebacks in unified metadata cache can be 1.47X higher than those with separate metadata caches on average.

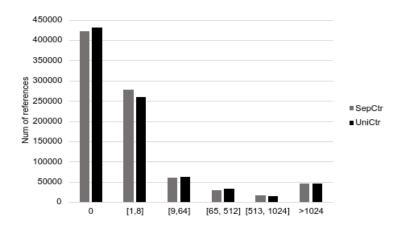

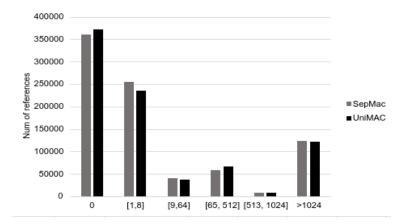

We also study the reuse distance of metadata in GPU secure memory. We choose the benchmark fdtd2d as our case study and present the reuse distance distribution of its counter and MAC accesses in Fig. 2.9 and Fig. 2.10, respectively. With the unified cache, we first collect the metadata access trace from partition 0 and extract sub-traces for each type of metadata. Then we compute the reuse distance based on the sub-traces. The references are grouped into different reuse distance buckets, where [x,y] means the reuse distance between x and y. From the figure, we can see that since GPUs feature streaming data access pattern, the metadata also shows a streaming pattern as most metadata accesses have a reuse distance of zero (i.e., accessing the same metadata cache line). In addition, with unified metadata caches, the counter and MAC accesses show higher numbers of accesses with reuse distances between 1 and 8. This indicates that higher capacities are required to capture these reuses using unified caches compared to separate caches. Note that accesses with small reuse distances (e.g., 0) do not always result in cache hits. The reason is that if the first access is a miss and the data has not been fetched, subsequent

accesses to the same cache line become secondary misses.

Overall, our conclusion is that for streaming data access patterns, we may either use separate metadata caches or adopt smart replacement policies to avoid the thrashing behavior. Note that the thrashing-avoiding replacement policies proposed for CPU lastlevel caches may not be readily adopted. The reason is that each newly fetched metadata block may be accessed multiple times as each metadata block protects multiple data blocks. For example, one MAC block contains MACs for 16 data blocks, with perfectly streaming accesses, the MAC block will be reused for 16 times.

Figure 2.7: Normalized IPC of unified metadata caches vs separate metadata caches.

Figure 2.8: Miss rates for different types of metadata in unified vs. separate metadata caches.

Figure 2.9: Reuse distance of counters of the benchmark fdtd2d

Figure 2.10: Reuse distance of MACs of the benchmark fdtd2d

## 2.3.5 AES Engine Throughput

To achieve high-throughput computation, GPUs usually have high requirements for the memory bandwidth. For example, our baseline GPU has a peak memory bandwidth of 868 GB/s. So far, we have assumed that each memory partition can be equipped with 2 pipelined AES engines such that the encryption throughput can catch up with the memory bandwidth. In this case, there would be a total of 64 (=2\*32) AES engines residing on the GPU chip.

To analyze the performance impact with different numbers of AES engines for each memory partition/unit, we reduce the number of AES engines in each memory partition/unit from 2 to 1 and the performance results are shown in Fig. 2.11. From the figure, we can see that although some benchmarks such as b+tree and kmeans observe a little performance degradation, most of the benchmarks are not affected by having just one pipeline AES engine in each memory partition. The reason is that for benchmarks with relatively low memory utilization, neither the memory bandwidth nor the AES throughput is the performance bottleneck. For the workloads with high memory bandwidth utilization, the performance bottleneck is the extra memory traffic generated by metadata accesses. Only after the memory bottleneck is addressed, the limitation due to AES throughput may be exposed. Some memory-intensive benchmarks, such as srad\_v2, streamcluster, 2Dconvolution, fdtd2d and lbm also exhibit slight performance improvement when the number of AES engines is reduced from 2 to 1. The reason is that these benchmarks have relatively high memory bandwidth utilization and large numbers of metadata write backs. Delaying some memory accesses due to limited AES throughput leads to a change in warp scheduling decisions as well as the cache access patterns, which results in small performance increase.

Figure 2.11: Normalized IPC with different numbers of AES engines in each memory partition

#### 2.3.6 Die Area

GPUs are highly-parallel processors, and most of their die area is dedicated for computational resources such as SIMT cores. For example, our baseline GPU models Nvidia Quadro

| -              | Tech  | Die Area            |

|----------------|-------|---------------------|

| JSSC'11[Mat11] | 45nm  | 0.15mm <sup>2</sup> |

| JSSC'19[Sin19] | 130nm | $13241 \mu m^{-2}$  |

| JSSC'20[Kum20] | 14nm  | $4900  \mu m^{ 2}$  |

Table 2.6: Die area of the AES engine

Table 2.7: Scaled down die area of the AES engine and caches

| -          | Area(mm <sup>2</sup> )/tech | Area(mm <sup>2</sup> )/12nm |

|------------|-----------------------------|-----------------------------|

| AES engine | 0.0049/14nm                 | 0.0036                      |

| 64KB cache | 0.125821/32nm               | 0.01769                     |

| 96KB cache | 0.128101/32nm               | 0.01801                     |

GV100, which is fabricated using 12nm FinFET Nvidia (FNN) technology with 21.1 billion transistors integrated on a die with the size of 815mm<sup>2</sup> [Jia18]. It integrates 80 SMs and each SM has 64 FP32 cores, 32 FP64 and 8 Tensor cores, which means a total of 5120 FP32 cores, 2560 FP64 cores and 640 Tensor cores.

To evaluate the die area required for counter-mode encryption, we estimate the area of both AES engine and the metadata caches. We list the results from prior works on AES design in Table 2.6 and scale the most recent design [Kum20] to the 12nm technology as shown in Table 2.7. From the table, we can see that the area of one AES engine is estimated as 0.0036 mm<sup>2</sup>. As there are 32 memory partitions, the total area for 32/64 AES engines is 0.1152/0.2304 mm<sup>2</sup>.

We use CACTI v6.5 to estimate the die area for the caches. As CACTI reports the area estimation using the 32nm technology, we also scale the results down to the 12nm technology, as shown in Table 2.7. As CACTI does not support modeling of small caches like 2KB, we report the area estimate of 64KB as 64KB is the aggregated capacity of one type of metadata caches in 32 partitions.

To make room for the die area required by the AES engines and metadata caches, we choose to reduce the L2 cache size. Since each L2 bank is 96KB, we also use CACTI to estimate the area. To accommodate 32 AES engines, the L2 cache capacity would need to be reduced by  $0.1152 \text{ mm}^2/0.01801 \text{ mm}^{2*}96\text{KB} = 614\text{KB}$ . Similarly, the metadata caches will occupy  $0.01769*3 = 0.05307 \text{ mm}^2$  on chip area, and hence reducing the L2 capacity by 0.05307/0.01801\*96KB = 283KB. If we assume MAC units have similar die area compared to AES engines, the security related hardware resources will reduce the L2 capacity by 614+614+298 = 1526KB in total (24.84% L2 cache capacity).

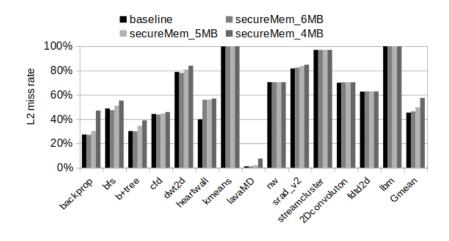

Figure 2.12: Normalized IPC with different L2 cache capacities

To evaluate the performance impact of the reduced L2 capacity, Fig. 2.12 shows the normalized performance for different L2 cache sizes, ranging from 4MB to 6MB. From the figure, we can see that although many benchmarks are not sensitive to the L2 cache capacity, a few of them show relatively high performance degradation. To better understand the reasons, we also report the L2 cache miss rate in Fig. 2.13. From the figure, we can see that some medium-memory-intensive benchmarks show high sensitivity to L2 capacity. It is expected since computation-intensive benchmarks (e.g., heartwall and lavaMD) have small numbers of L2 accesses whereas highly memory intensive benchmarks such as lbm or fdtd2d have very high L2 miss rates. Changing L2 capacity has little impact on these workloads.

Figure 2.13: L2 cache miss rate

| Scheme        | What It Represents                   |

|---------------|--------------------------------------|

| direct_x      | direct encryption with different en- |

|               | cryption latency of x cycles         |

| ctr           | counter-mode memory encryption       |

|               | without any integrity protection     |

| ctr_bmt       | counter-mode encryption with BMT     |

|               | to protect counter integrity         |

| ctr_mac_bmt   | counter-mode encryption with BMT     |

|               | and MACs                             |

| direct_mac    | direct encryption with MACs.         |

| direct_mac_mt | direct encryption with MACs and MT.  |

Table 2.8:Evaluated designs for direct encryption

## 2.4 Direct Encryption

In this section, we evaluate direct encryption and explore the option of different levels of integrity protection. The designs that we evaluate in this section are listed in Table 2.8.

## 2.4.1 Performance Overheads of Direction Encryption

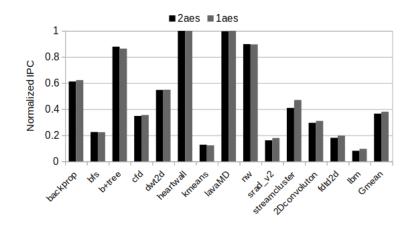

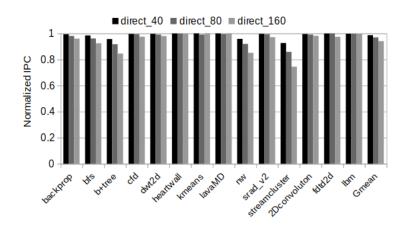

As direct encryption exposes the decryption latency to the critical path of memory read accesses, it can slowdown the performance heavily on CPUs [Yan03]. However, GPUs are designed for high-throughput computation by exploiting the high degrees of TLP. Hence, GPUs are able to tolerate long operation latency. It is expected that adding some encryption latency to the memory access would not hurt the GPU performance significantly.

Figure 2.14: Normalized IPC of direct encryption with different encryption latencies.

We model the direct encryption with different encryption/decryption latencies upon our baseline GPU and the performance results are shown in Fig. 2.14. As expected, direct encryption does not affect the GPU performance much. When the encryption latency varies from 40 cycles to 160 cycles, the IPC slowdown is 1.33%, 3.02%, 5.93%, respectively on average. Some benchmark, e.g., b+tree, nw and streamcluster, show more than 10% slowdowns at the high encryption latency of 160 cycles. The reasons are different among these three benchmarks: (1) benchmark streamcluster suffers from high L2 miss rate (97.02%) as shown in Fig. 2.13, which leads to many memory read accesses, (2) benchmark nw is limited by the small kernel (shown in Table 2.4) such that they do not have enough threads to hide the encryption latency. (3) benchmark b+tree shows interesting results because it's neither bounded by kernel size nor L2 miss rate. Digging deeper, we find that with a high encryption latency of 160 cycles, b+tree suffers from 2.42X dram stall time compared the baseline GPU. Our results show that given longer dram stall time, all the available warps in b+tree suffer 12.2% more pipeline cycles to wait data from memory on average, and thus slowdown the performance. Although high encryption/decryption latency does not impact the GPU performance significantly, we choose 40 cycles as the default encryption/decryption latency, which is consistent with prior work on AES encryption for CPUs [Leh18].

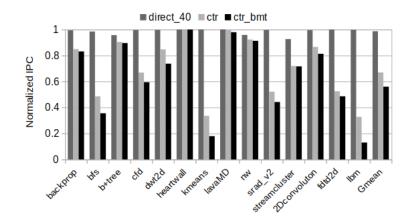

Figure 2.15: Normalized IPC of direct encryption and counter-mode encryption

#### 2.4.2 Direct Encryption vs. Counter-mode Encryption

To better understand the trade-offs between direct encryption and counter-mode encryption, we examine their performance in Fig. 2.15. From Fig. 2.15, we can make two observations. First, as discussed above, the performance impact of direct encryption is almost negligible. Second, compared with direct encryption, counter-mode encryption without integrity checks can lead to a relatively high performance overhead (33.06% on average, and up to 66.44% for the memory-intensive workload lbm). As we studied in section 2.3, the main reason is that counter-mode encryption will generate additional memory traffic to fetch/store counters from/to the off-chip main memory.

Moreover, as we discussed in Chapter 1 section 1.2.2, counter-mode encryption *fundamentally relies* on counter integrity protection to provide data confidentiality. The reason is that the counters are used for encryption and decryption. Without integrity checks of the counters, the GPU cannot tell whether a counter has been altered by the attacker or not. In this case, an attacker may be able to manipulate the counters to recover the plaintext. It can be illustrated as follows. Let us use *P* as the plaintext, *C* as the ciphertext, and *K* as the secret key of AES. Then the ciphertext is generated by  $C = E_K(A||Ctr) \oplus P$ , where *A* is the address of the memory block and Ctr is the counter. *P* can be recovered with  $C \oplus E_K(A||Ctr)$  if Ctrcan be controlled by the attacker. Hence, with counter-mode encryption, BMT is needed anyway to provide integrity protection to the counters stored in the off-chip memory.

As we can see from Fig. 2.15, adding the integrity protection to counters further increases the performance overhead, 43.94% on average for all the benchmarks in our study.

In summary, our evaluation suggests that if the memory only needs to be encrypted, direct encryption would be a better choice for GPUs.

#### 2.4.3 Integrity Protection

Memory encryption can provide data confidentiality. However, it cannot provide memory integrity protection when the attackers have the ability to tamper the memory contents. With counter-mode encryption, data integrity protection is provided by stateful MACs, and counter integrity protection is provided by BMT. With direct encryption, one can choose to build MAC upon cyphertext with/without a Merkle Tree (MT). The MT is needed to prevent replay attacks and can be built with the MACs as its leaf nodes.

We model these schemes and compare the performance results in Fig. 2.16. For fairness, we assume the same on chip resource used by the metadata caches. In counter-mode

encryption, as mentioned in Section 2.3, a 2KB on-chip metadata cache is used for each type of metadata and a total of 6KB on-chip resource is used in each memory partition. In direct encryption with MAC, we model a MAC cache with the size of 6KB. In direct encryption with both MAC and MT, we model a 3KB MAC cache and 3KB MT cache (the MACs will not access the MT cache as they are cached in the MAC cache).

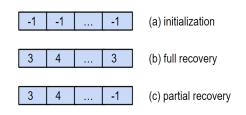

Figure 2.16: Normalized IPC of direct encryption and counter-mode encryption with integrity protection