#### **ABSTRACT**

RAMANAN, NARAYANAN. Investigation of ALD Dielectrics for Improved Threshold Voltage Stability and Current Collapse Suppression in AlGaN/GaN MOS-HFETs. (Under the direction of Dr. Veena Misra).

Owing to a high critical electric field and high electron mobility, GaN based lateral Heterojunction Field Effect Transistors (HFETs) are sought after for high voltage power and RF applications. But, device reliability continues to be a critical challenge to be overcome before successful commercialization. In this work, different dielectrics deposited by Atomic Layer Deposition are investigated for improving the threshold voltage stability and dynamic reliability of AlGaN/GaN based Metal-Oxide-Semiconductor-HFETs (MOS-HFETs). But more importantly, this work includes a first-of-its-kind comprehensive analysis of electrical characterization techniques and physics-based models required to evaluate and recommend any dielectric for mitigating surface trapping phenomena in the gate stack or the access-regions.

In an investigation of the impact of MOSHFET device structure on the efficacy of different methods for characterization of dielectric/AlGaN interface traps, it is found that the popular conductance method has a severely constrained detection limit when the AlGaN barrier offers high resistance to the de-trapping electrons. A capacitance-based method is immune to the issue of barrier resistance, but is still restrictive in its range. To improve the range and accuracy of trap detection, a novel pulsed-IV-based methodology is developed and demonstrated to be applicable for detecting both shallow and deep traps.

Identical electrical thickness of different high-k and low-k ALD dielectrics are evaluated for gate leakage and magnitude and stability of threshold voltage. It is established that the high-k dielectrics (Al<sub>2</sub>O<sub>3</sub>, HfO<sub>2</sub> and HfAlO) harbor a high density of shallow traps at the dielectric/AlGaN interface. In contrast, ALD SiO<sub>2</sub>, annealed in N<sub>2</sub> at 700°C, creates a very low density of interface traps (< 2×10<sup>12</sup> cm<sup>-2</sup>) and is an excellent candidate for a gate dielectric. It provides strong gate leakage suppression, minimal threshold voltage shift and highly reliable ON-state characteristics.

With the use of physics-based simulation models, it is identified that the leakage at the surface of the AlGaN, whether through the passivation dielectric bulk or the dielectric/AlGaN interface, must be minimized to restrict the formation of a "virtual gate" and minimize current collapse. An optimal passivation dielectric must also create a high density of shallow interface donor traps to quicken the de-trapping of electrons from the "virtual gate" and the recovery of the channel underneath.

In order to create a high density of shallow interface donor traps a thin ALD HfAlO film is used. Surface leakage is also minimized by capping with a thick layer of PECVD  $SiO_2$  and annealing in  $N_2$  at  $700^{\circ}$ C. The effectiveness of the resulting optimal dual dielectric passivation stack in mitigating current collapse and ensuring contact isolation is also demonstrated.

Therefore, the optimal ALD dielectrics for a reliable gate stack and access-region passivation in an AlGaN/GaN MOSHFET are identified to be  $SiO_2$  and HfAlO, respectively, annealed at  $700^{\circ}$ C in  $N_2$ .

© Copyright 2014 by Narayanan Ramanan

All Rights Reserved

## Investigation of ALD Dielectrics for Improved Threshold Voltage Stability and Current Collapse Suppression in AlGaN/GaN MOS-HFETs

#### by Narayanan Ramanan

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the degree of Doctor of Philosophy

**Electrical Engineering**

Raleigh, North Carolina 2014

APPROVED BY:

| Dr. Veena Misra  | Dr. John Muth    |

|------------------|------------------|

| Committee Chair  |                  |

|                  |                  |

|                  |                  |

|                  |                  |

| Dr. Griff Bilbro | Dr. Zlatko Sitar |

#### **DEDICATION**

"We are always surrounded by ignorance at some level or another. If you are going to assign God to that ignorance and you lose your curiosity to investigate it, solutions will always elude you."

- Neil deGrasse Tyson in *The Inexplicable Universe with Neil deGrasse Tyson*

Dedicated to all my teachers and, in particular, my gurus of Physics, Prof. R. Ananthan and Mr. C. S. Ravi Shankar, who nurtured my curiosity to investigate and never give up.

Prof. R Ananthan

Mr. C. S. Ravi Shankar

#### **BIOGRAPHY**

#### Vita:

1986 Born in Chandigarh, India

Aug. 2004 – July 2009 B. Tech in Electrical Engineering,

M. Tech in Power Systems and Power Electronics,

Indian Institute of Technology-Madras, Chennai, India

Aug. 2009 – Sep. 2014 Ph.D. in Electrical Engineering,

North Carolina State University, Raleigh, NC, USA

#### **Publications:**

[1] N. Ramanan, B. Lee and V. Misra, "Comparison of Methods for Accurate Characterization of Interface Traps in GaN MOS-HFET Devices," to be submitted to *IEEE Trans. Electron Devices*, Sep 2014.

- [2] N. Ramanan, B. Lee and V. Misra, "ALD Dielectrics for Improved Gate Stack and Passivation Reliability of AlGaN/GaN MOS-HFETs in power Applications," to be submitted to *IEEE Electron Device Lett.*, Sep. 2014.

- [3] N. Ramanan, B. Lee and V. Misra, "Device Modeling for Understanding AlGaN/GaN HEMT Gate Lag," *IEEE Trans. Electron Devices*, vol. 61, no. 6, pp. 2012-2018, June 2014.

- [4] N. Ramanan, B. Lee and V. Misra, "A Novel Methodology using Pulsed-IV for Interface of Border Traps Characterization on AlGaN/GaN MOSHFETs," *IEEE* 26<sup>th</sup> *Int. Symp. On Power Semiconductor Devices and IC's (ISPSD)*, Hawaii, pp. 366-369, 15-19 June 2014.

- [5] C. Kirkpatrick, B. Lee, N. Ramanan and V. Misra, "Flash MOS-HFET operational stability for power converter circuits," *physica status solidi* (*c*), vol. 11, no. 3-4, pp. 875-878, April 2014.

- [6] B. Sarkar, N. Ramanan, S. Jayanti, N. Di Spigna, B. Lee, P. Franzon and V. Misra, "Dual Floating Gate Unified Memory MOSFET with Simultaneous Dynamic and non-volatile operation," *Electron Device Lett.*, vol. 35, no. 1, pp. 48-50, Dec. 2013.

- [7] N. Ramanan, B. Lee, C. Kirkpatrick, R. Suri and V. Misra, "Properties of atomic layer deposited dielectrics for AlGaN/GaN device passivation," invited in *Semiconductor Sci. Technology*, vol. 28, no. 7, pp. 074004, 2013.

- [8] N. Ramanan and V. Misra, "Multivalued Logic using a Novel Multichannel GaN MOS Structure," *IEEE Electron Device Lett.*, vol. 32, no. 10, pp. 1379-1381, 2011.

- [9] N. Ramanan, S. Khatchadourian, J-C. Prevotet and L. Kessal, "Neural Network Hardware Architecture for Pattern Recognition in the HESS2 Project," *Proceedings of European Symposium on Artificial Neural Networks*, Bruges, Belgium, 23-25 April 2008. Available. [Online]. <a href="https://www.elen.ucl.ac.be/Proceedings/esann/esannpdf/es2008-107.pdf">https://www.elen.ucl.ac.be/Proceedings/esann/esannpdf/es2008-107.pdf</a>

#### **ACKNOWLEDGMENTS**

There are some things in life beyond your grasp of understanding. Fate is one among them. Some people call it coincidence, others providence. Whatever it is, I am thankful to all the good souls who have helped me through my journey and contributed one way or another in making my stay at NCSU a fulfilling experience.

My first thanks are due to the J. N. Tata Endowment for helping finance my first semester at NCSU. I may not have taken the big step of studying abroad, if not for them.

I am deeply indebted to my advisor Dr. Veena Misra, for having faith in me and providing me the opportunity to work on this exciting research project. She has been a great mentor, always lending a keen ear to my troubles and offering her guidance, all the while letting me choose my own path. She is undeniably, my role model of a dedicated scientist who is also a great human being.

I would like to also thank Dr. John Muth, Dr. Griff Bilbro and Dr. Zlatko Sitar for serving on my committee and offering critical comments and feedback. Special thanks go to Dr. Bongmook Lee and Dr. Casey Kirkpatrick for introducing me to the weird world of GaN and providing all the training I needed for device fabrication and characterization. Dr. Lee has always been my first 'go-to' person whenever I have had trouble in my research, and somehow, he almost always has an answer to everything!

I express my sincere appreciation to the staff members of the NCSU Nanofabrication Facility (NNF) and the Shared Materials Instrumentation Facility (SMIF) at Duke University. Without their dedicated efforts in keeping the cleanroom facilities functional, I would have gone nowhere. © I would also like to acknowledge the help and support of my past and present group members Dr. Srikant Jayanti, Dr. Rahul Suri, Dr. Steven Novak, Xiangyu Yang, Steven Mills, Michael Lim and Biplab Sarkar. A lot of my work is inspired from discussions we have shared regarding device physics, processes and characterization

techniques. They have also been hugely responsible for maintaining all our lab equipment with sincere dedication.

Although I express my sincere gratitude to Dr. Rama Vetury for giving me the opportunity of working with him as an intern at RFMD, Charlotte, NC, I only wish I had more time to spend under his mentorship. His PhD dissertation, submitted in 2000 at UC Santa Barbara, was instrumental in giving me insights of the phenomenon of current collapse in GaN, which is also the main focus of this work. I learnt a lot about the GaN industry during my short time at Charlotte, but there is still so much more to learn from him.

There is no way I can fully repay the unconditional love and affection showered by parents and my "motherly" sister. I am also blessed with caring cousins, uncles and aunts who never stop appreciating and encouraging all my endeavors. For some unknown reason, they all have blind faith in whatever I do. © I hope I have done them justice with this work.

I have made a lot of friends in Raleigh and cherished some of my best moments with them here. Most notably, the Sivaji gang, with Dr. Vikram Seshadri and Dr. Rajagopal Panchapakesan. We rocked! And I hope we continue our good run in the future. I have a lot of fond memories of the times with my roommates, Dr. Vikram Seshadri and Dr. Mahendra Dia, and have learnt a lot from them. Special thanks also go to Vinodh Kotipalli, Ayush Jain, Biplab Sarkar and Amir Hassani for 'tolerating' me through this time. I would also like to thank Dr. Gayatri Venugopal, Anirudh Venugopal, Bharath Sampath, Sudarshan Nallan Chakravarthy, Sahil Dahiya, Sudarshan Prasad, Vivek Devarajan, Srikrishna Gopu and Sankalp Nimbhorkar for making this place a home, away from home. I also owe gratitude to Dr. Vijay Srinivasan and his wife Jayalakshmi Narasimhan for offering me their beautiful home to stay and peacefully write my dissertation during the final stages of my stay.

Finally, I would like to express my gratitude to Dr. Paul Maki, at the Office of Naval Research (Award No. N00014-11-1-0945), and National Science Foundation (Award No. ERC FREEDM EEC-08212121) for the funding and RFMD for some of the GaN substrates used in this work.

## TABLE OF CONTENTS

| LIST OF TABLES                                                                    | X  |

|-----------------------------------------------------------------------------------|----|

| LIST OF FIGURES                                                                   |    |

|                                                                                   |    |

| CHAPTER 1: Introduction                                                           |    |

| 1.1 Overview of GaN based electronics market                                      |    |

| 1.2 Background of lateral GaN device physics                                      | 6  |

| 1.3 Technical challenges to lateral GaN device adoption                           | 8  |

| 1.3.1 Challenges associated with access regions                                   | 9  |

| 1.3.2 Challenges associated with gate stack                                       |    |

| 1.4 Key technological solution: Dielectrics deposited by Thermal Atomic Layer Dep |    |

|                                                                                   |    |

| 1.5 Dissertation goals and organization                                           | 14 |

| CHAPTER 2: Experimental Methods                                                   | 16 |

| 2.1 Transistor Fabrication                                                        |    |

| 2.1.1 Substrate properties                                                        | 16 |

| 2.1.2 Atomic Layer Deposition (ALD) process                                       |    |

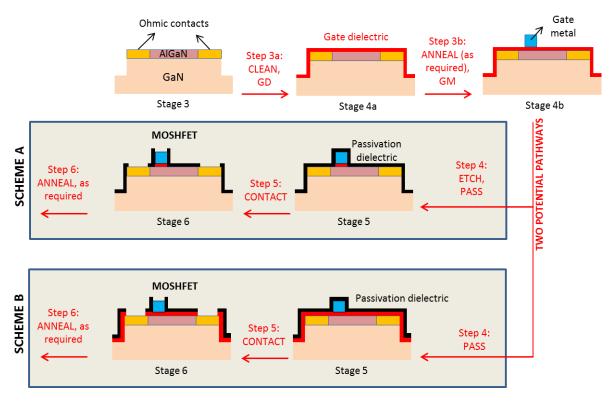

| 2.1.3 HFET fabrication flow                                                       | 18 |

| 2.1.4 MOSHFET fabrication flow                                                    |    |

| 2.2 Characterization Equipment                                                    |    |

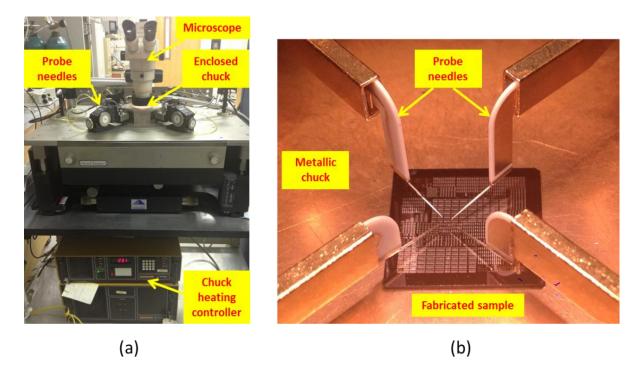

| 2.2.1 Cascade probe-station                                                       |    |

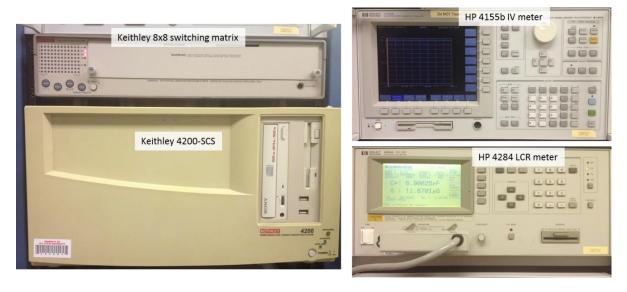

| 2.2.2 DC I-V and LCR meters                                                       |    |

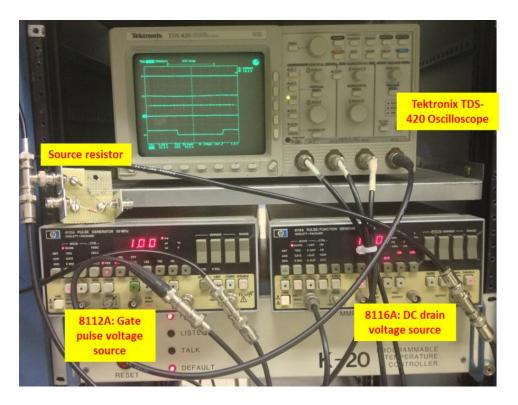

| 2.2.3 Pulsed-IV meter                                                             | 23 |

|                                                                                   |    |

| CHAPTER 3: Methods for Accurate Characterization of Interface                     | _  |

| in GaN MOSHFET Devices                                                            |    |

| 3.1 Introduction                                                                  |    |

| 3.2 Background                                                                    |    |

| 3.2.1 Fabrication Flow                                                            |    |

| 3.2.2 Simulation Framework                                                        |    |

|                                                                                   |    |

| 3.3 Theoretical Comparison of Interface Trap Characterization Methods             |    |

| 3.3.2 Capacitance Method                                                          |    |

| 3.3.3 Pulsed-IV Method                                                            |    |

| 3.3.4 Inferences                                                                  |    |

| 3.4 Experimental Demonstration of Accurate Interface Trap Characterization        |    |

| 3.4.1 Introduction                                                                |    |

| 3.4.2 Quasi-steady state characterization                                         | 45 |

| 3.4.3 Trap density measurement                                             | 45         |

|----------------------------------------------------------------------------|------------|

| 3.4.4 Trap depth estimation                                                | 47         |

| 3.4.5 Final trap density profile reconstruction and validation             | 49         |

| 3.5 Summary                                                                |            |

| CHAPTER 4 : Characterization of Traps at ALD Dielectric/AlC                | Ga N       |

| Interface                                                                  |            |

| 4.1 Introduction                                                           |            |

| 4.2 Sample preparation                                                     |            |

| 4.3 Extraction of gate stack capacitance                                   |            |

| 4.4 Interface traps at ALD HfO <sub>2</sub> /AlGaN interface               |            |

| 4.5 Interface traps at ALD HfAlO/AlGaN interface                           |            |

| 4.6 Interface traps at ALD Al <sub>2</sub> O <sub>3</sub> /AlGaN interface |            |

| 4.7 Interface traps at ALD SiO <sub>2</sub> /AlGaN interface               |            |

| 4.8 Interface traps at PECVD silicon nitride/AlGaN interface               |            |

| 4.9 Summary                                                                |            |

| CHAPTER 5 : ALD Dielectrics for Gate Stack                                 | <i>(</i> 1 |

|                                                                            |            |

| 5.1 Introduction                                                           |            |

| 5.2.1 Introduction                                                         |            |

| 5.2.2 Gate leakage trends                                                  |            |

| 5.3 ON-state gate stack reliability                                        |            |

| 5.4 MOSHFET threshold voltage                                              |            |

| 5.4.1 Influence of gate dielectric on threshold voltage                    |            |

| 5.4.2 Threshold voltage trends                                             |            |

| 5.5 Summary                                                                |            |

| CHAPTED ( . Dale of Sunface Descivation for Improved Access                | Dagian     |

| CHAPTER 6 : Role of Surface Passivation for Improved Access Reliability    | _          |

| 6.1 Introduction                                                           |            |

| 6.2 Gate-lag measurement: A window into surface trapping                   |            |

| 6.3 Impact of passivation dielectric on gate-lag                           |            |

| 6.3.1 Introduction                                                         |            |

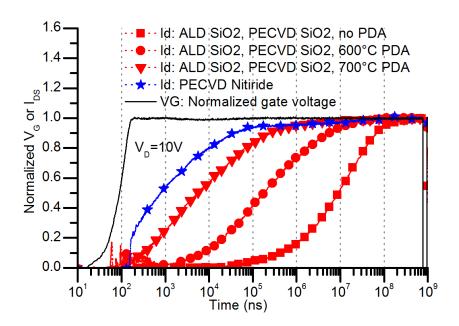

| 6.3.2 Preliminary experiment 1                                             |            |

| 6.3.3 Preliminary experiment 2                                             |            |

| 6.3.4 Preliminary conclusions                                              |            |

| 6.4 Device Modeling for Understanding AlGaN/GaN HEMT Gate-Lag              |            |

| 6.4.1 Introduction                                                         |            |

| 6.4.2 Simulation Framework                                                 |            |

| 6.4.2.1 Background                                                         |            |

| 6.4.2.2 Model development                                                  |            |

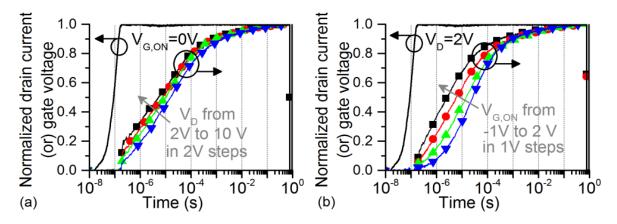

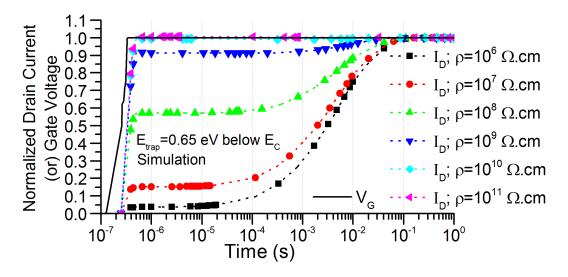

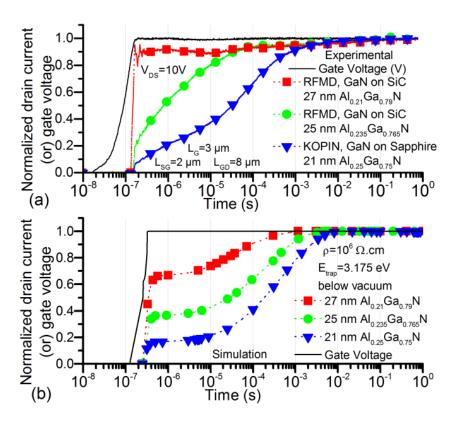

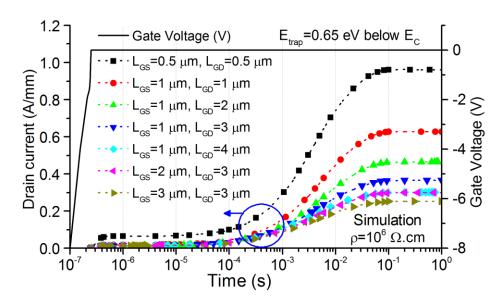

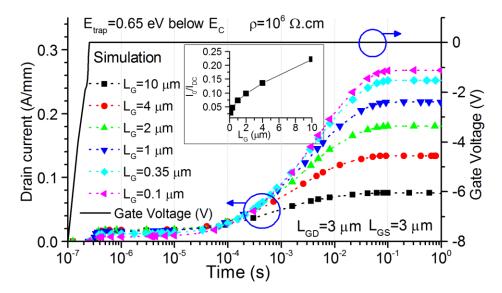

| 6.4.2.3 Gate-lag simulation                                                | 82         |

|                                                                            |            |

| 6.4.3 Modeling results                                   | 82  |

|----------------------------------------------------------|-----|

| 6.4.3.1 Passivation dielectric                           | 82  |

| 6.4.3.2 Barrier material properties                      | 89  |

| 6.4.3.3 HFET structure                                   |     |

| 6.5 Summary                                              |     |

| CHAPTER 7: ALD Dielectrics for Access-Region Reliability | 94  |

| 7.1 Introduction                                         |     |

| 7.2 ALD dielectrics for HFET passivation                 |     |

| 7.3 ALD dielectrics for MOSHFET passivation              |     |

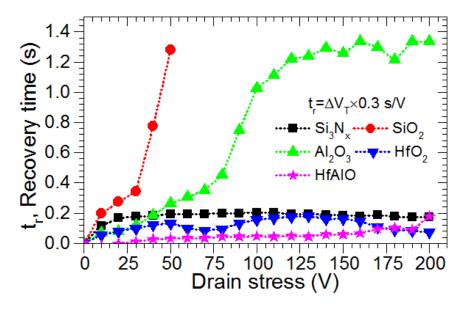

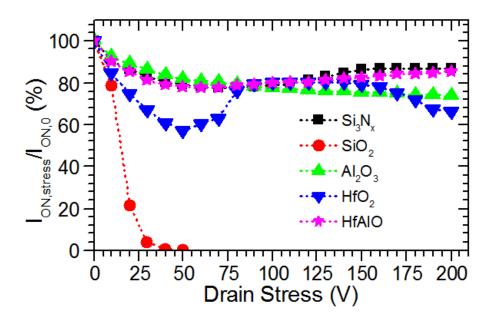

| 7.3.1 Drain stress measurements                          |     |

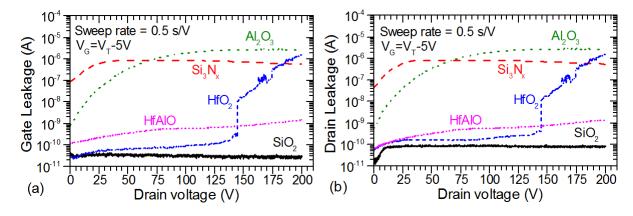

| 7.3.2 Gate-drain isolation                               |     |

| 7.4 Summary                                              |     |

| CHAPTER 8 : Conclusions and Future Work                  | 104 |

| 8.1 Conclusions                                          |     |

| 8.2 Future Work                                          |     |

| REFERENCES                                               | 110 |

## LIST OF TABLES

| Table 1.1: Material parameters of Si, SiC and GaN. Figures of Merit are normalized with        |

|------------------------------------------------------------------------------------------------|

| respect to Si [4], [5]                                                                         |

| Table 1.2: Key advantages of thermal ALD over other techniques for this dielectric reliability |

| investigation                                                                                  |

| Table 2.1: Properties of the AlGaN/GaN substrates used in this work                            |

| Table 2.2: ALD deposition conditions used for different dielectrics                            |

| Table 3.1: Parameters used for the MOS-HFET TCAD simulations                                   |

| Table 3.2: Summary of the pros and cons of different trap characterization methods:            |

| conductance (GV), capacitance (CV), pulsed-IV (PIV) and a combination of PIV                   |

| and GV (PIV+GV)                                                                                |

| Table 4.1: Thickness of different layers of the fabricated MOSHFETs                            |

| Table 4.2: Minimum total measured density of traps for different dielectrics and annealing     |

| conditions                                                                                     |

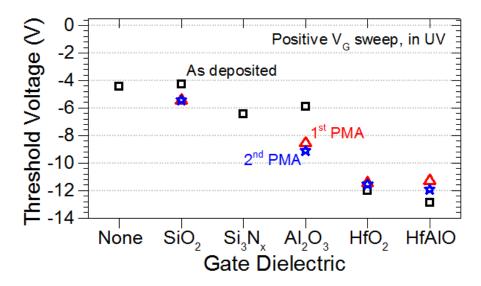

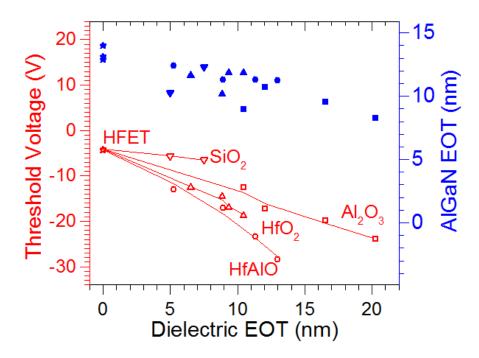

| Table 5.1: Interface and bulk charge densities extracted for different ALD dielectrics from    |

| measured values of threshold voltage from Figure 5.5 using (5.2)                               |

| Table 8.1: Simplistic comparison of performance of different ALD dielectrics evaluated in      |

| this work for use as a gate dielectric or as a thin passivation dielectric in a dual           |

| dielectric stack                                                                               |

## LIST OF FIGURES

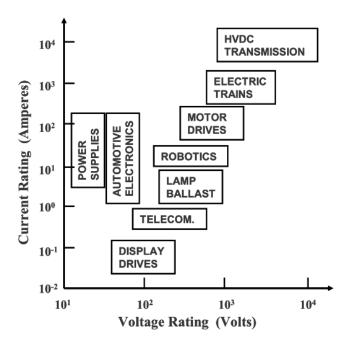

| Figure 1.1: | Typical voltage and current ratings of different electrical systems in use around        |

|-------------|------------------------------------------------------------------------------------------|

|             | us                                                                                       |

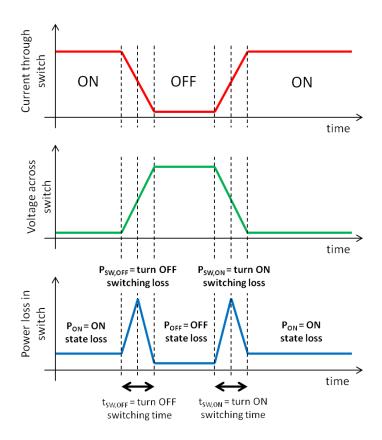

| Figure 1.2: | Simplified sketch of the typical transient waveforms of current, voltage and             |

|             | power loss in a power switch                                                             |

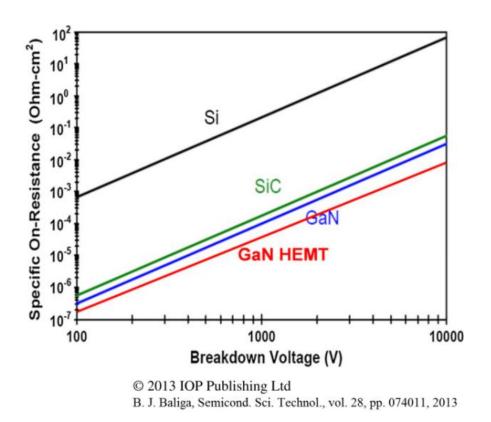

| Figure 1.3: | Comparison of ideal specific ON-resistance between different material systems            |

|             | over breakdown voltage                                                                   |

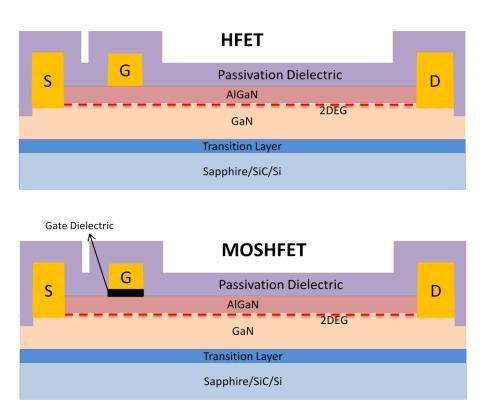

| Figure 1.4: | Simple schematic of an AlGaN/GaN based HFET and MOSHFET 6                                |

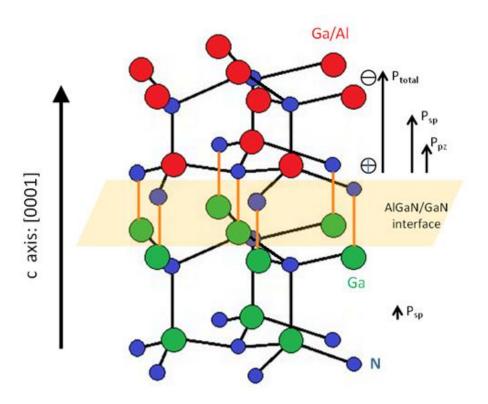

| Figure 1.5: | Crystal structure at the interface between AlGaN and GaN. Also shown are the             |

|             | polarization components and the resulting equivalent fixed charge at the AlGaN           |

|             | barrier boundaries                                                                       |

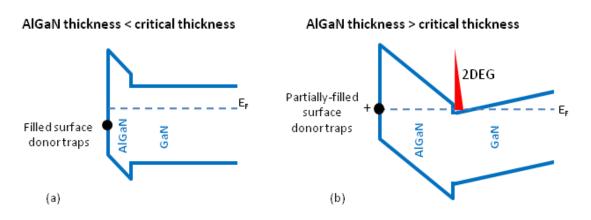

| Figure 1.6: | Conduction band diagram of an AlGaN /GaN HEMT device along the depth from                |

|             | the metal gate when the a) AlGaN barrier is thin, and b) AlGaN barrier is thick.         |

|             | Also shown is the resulting 2DEG at the AlGaN/GaN interface                              |

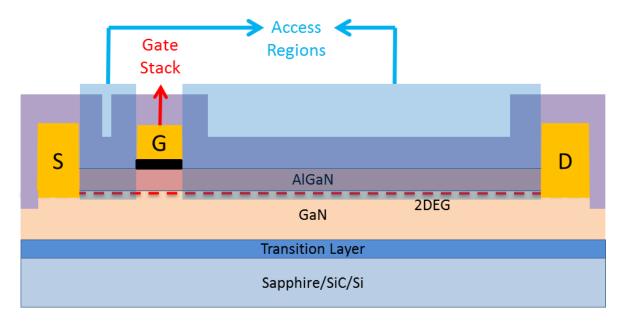

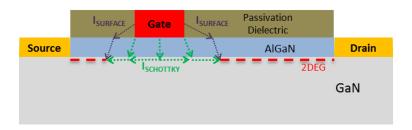

| Figure 1.7: | Simple schematic of an AlGaN/GaN based MOSHFET illustrating the locations                |

|             | of the gate stack and the access regions.                                                |

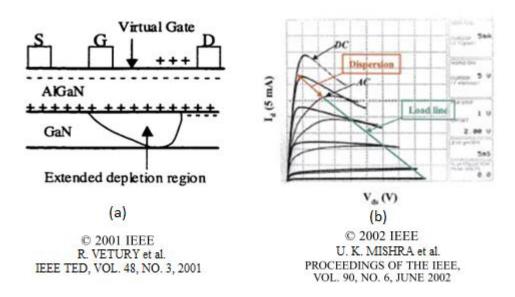

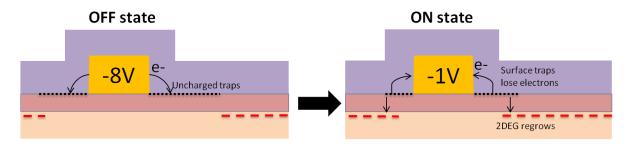

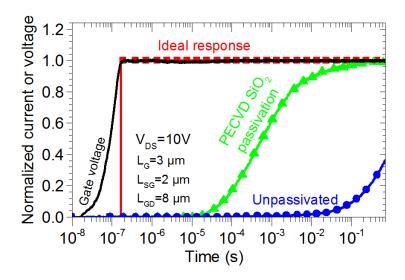

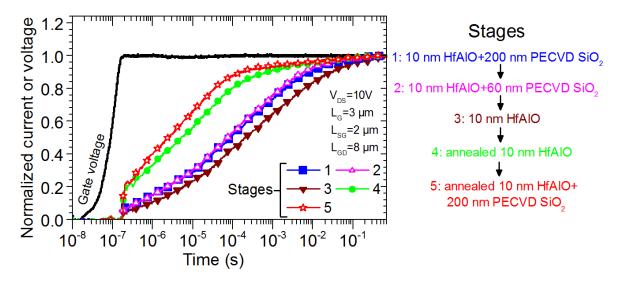

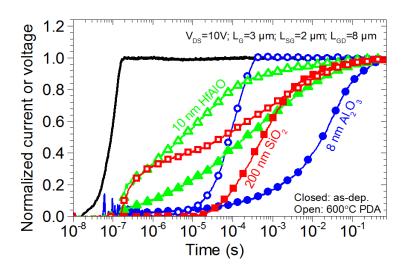

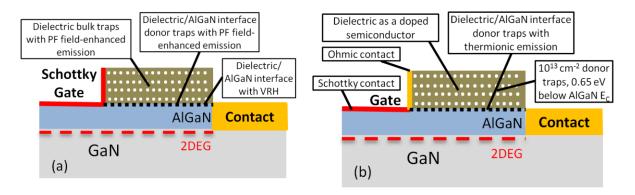

| Figure 1.8: | (a) Development of a virtual gate in an AlGaN/GaN HFET under the application             |

|             | of a high negative gate bias; (b) Typical current collapse between AC and DC,            |

|             | observed in an AlGaN/GaN HFET                                                            |

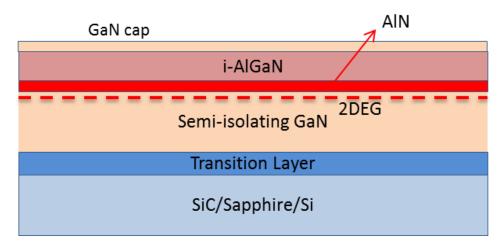

| Figure 2.1: | Simple schematic of the AlGaN/GaN substrates procured from vendors, as listed            |

|             | in Table 2.1                                                                             |

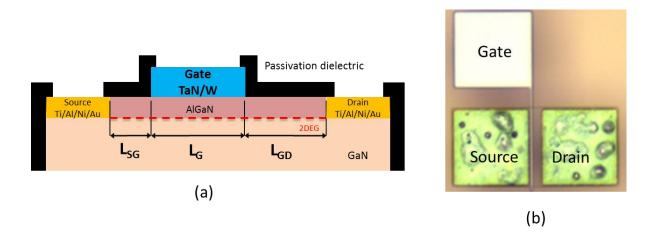

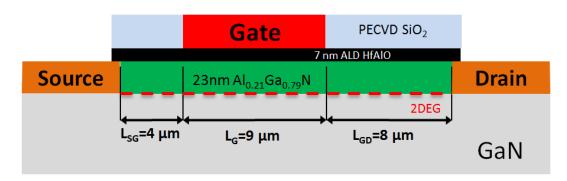

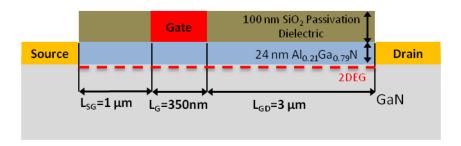

| Figure 2.2: | (a) Cross-sectional schematic of the fabricated HFET device. $L_{\text{GD}}=$ gate-drain |

|             | spacing; $L_G=$ gate length; $L_{SG}=$ gate-source spacing. (b) Top view image of the    |

|             | fabricated line device                                                                   |

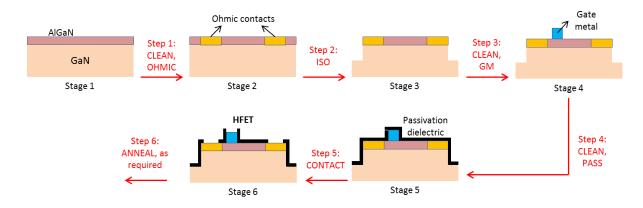

| Figure 2.3: | Simple schematic showing the HFET fabrication flow                                       |

| Figure 2.4: | Simple schematic showing the MOSHFET fabrication flow                                    |

| Figure 2.5: | (a) Picture of the Cascade on-wafer probe station with heated chuck. (b) Image of        |

|             | a fabricated sample under measurement in the probe station                               |

| Figure 2.6: | Equipment used for DC IV, CV and GV measurements                                                                            |

|-------------|-----------------------------------------------------------------------------------------------------------------------------|

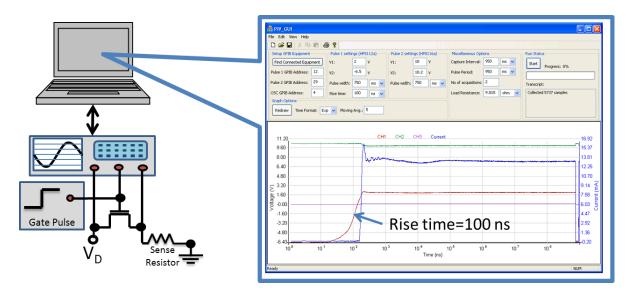

| Figure 2.7  | : Picture of the custom built pulsed-IV setup with a Tektronix TDS-420                                                      |

|             | oscilloscope and two HP pulse generators (HP 8112A, HP 8116A) as the voltage                                                |

|             | sources                                                                                                                     |

| Figure 2.8: | Simple schematic of the custom built pulsed-IV setup with an oscilloscope and a                                             |

|             | pulse generator                                                                                                             |

| Figure 3.1: | A cross section of the fabricated MOSHFET device with HfAlO gate dielectric                                                 |

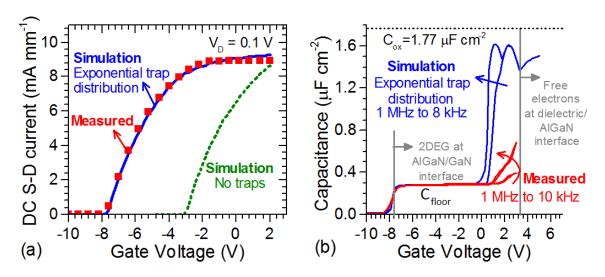

| Figure 3.2: | Measured and simulated $I_D$ - $V_G$ curves for the fabricated MOS-HFET 30                                                  |

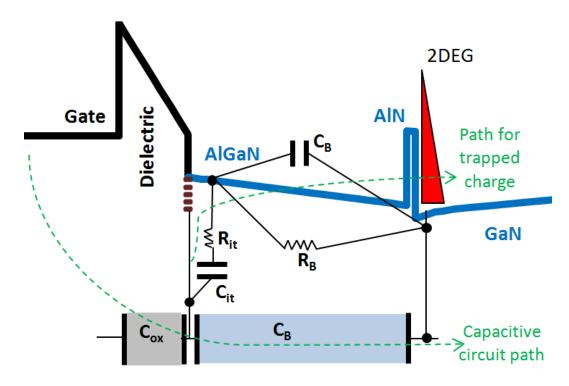

| Figure 3.3  | : Energy band diagram under the MOS-HFET gate stack, illustrating the                                                       |

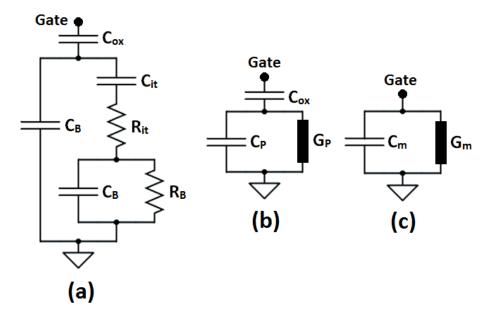

|             | construction of the equivalent small-signal circuit                                                                         |

| Figure 3.4: | Various representations of the MOS-HFET small-signal equivalent circuit: (a)                                                |

|             | same as Figure 3.3; (b) combines all the semiconductor components into ar                                                   |

|             | equivalent parallel capacitance and conductance, C <sub>P</sub> and G <sub>P</sub> ; (c) represents the                     |

|             | equivalent capacitance and conductance of the device as measured, $C_{\text{\scriptsize m}}$ and $G_{\text{\scriptsize m}}$ |

|             |                                                                                                                             |

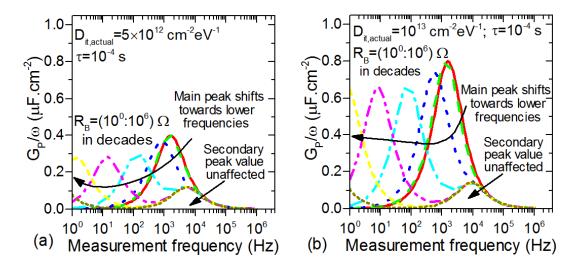

| Figure 3.5: | Conductance, $G_P/\omega$ , calculated for the circuit model in Figure 3.4a over a range of                                 |

|             | barrier resistance values, for two different trap densities: (a) $5 \times 10^{12}$ cm <sup>-2</sup> eV <sup>-1</sup>       |

|             | (b) $10^{13} \text{ cm}^{-2} \text{ eV}^{-1}$                                                                               |

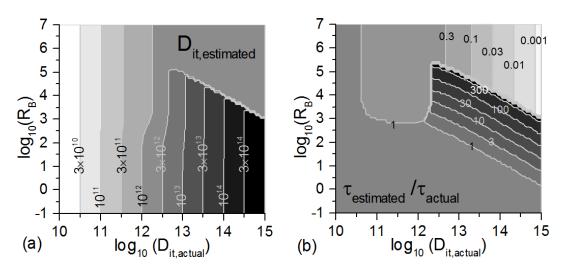

| Figure 3.6: | (a) Trap density, $D_{it}$ , and (b) error in the response time, $\tau$ , estimated from the peak                           |

|             | positions and values of the tallest peaks of the calculated conductance in the                                              |

|             | frequency range 1 Hz - 1 MHz. 35                                                                                            |

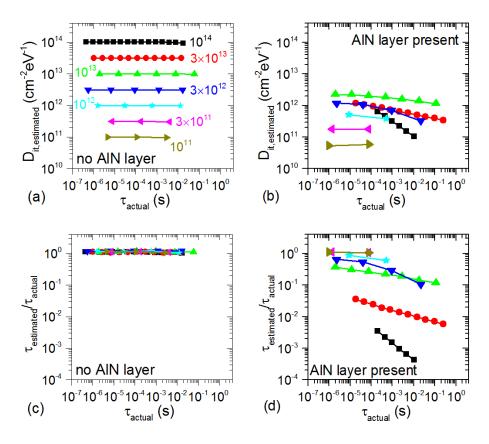

| Figure 3.7: | TCAD simulation results of the conductance method on the MOS-HFET device                                                    |

|             | with different interface trap densities distributed uniformly in energy: estimated                                          |

|             | trap density (a) without and (b) with AlN layer; error in the estimated trap                                                |

|             | response time (c) without and (d) with AlN layer                                                                            |

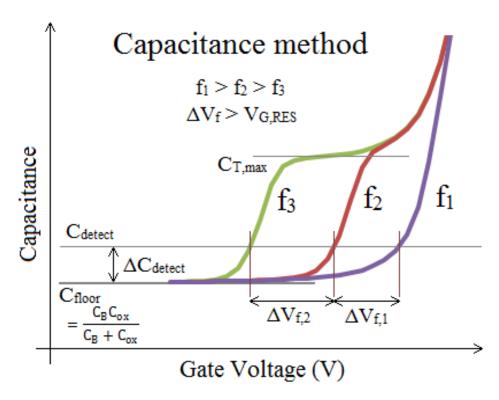

| Figure 3.8: | Schematic showing the extraction of the gate voltage shift, $\Delta V_{\text{f}}$ , of the second CV                        |

|             | step in Figure 3.2b, for the capacitance method of extracting interface trap                                                |

|             | density                                                                                                                     |

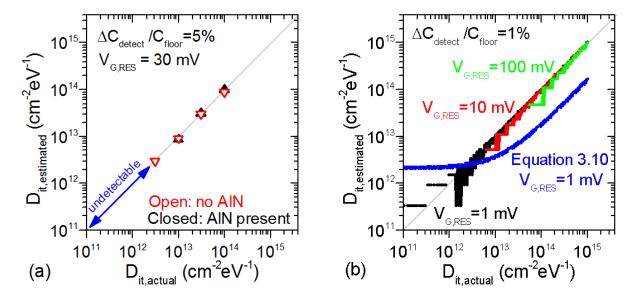

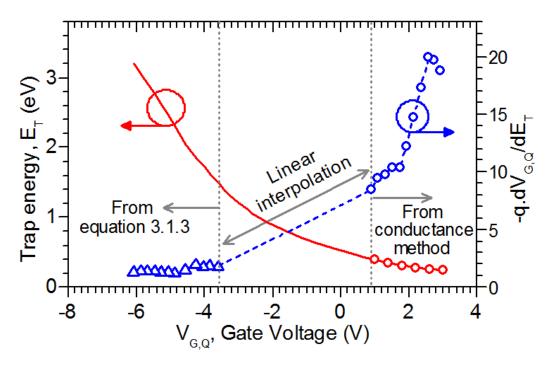

| Figure 3.9: (a) Trap density estimated using TCAD simulations of the capacitance method                            | d for            |

|--------------------------------------------------------------------------------------------------------------------|------------------|

| the barrier with/without the AlN layer. The lowest detectable trap density                                         | was              |

| $\approx 3 \times 10^{12}$ cm <sup>2</sup> eV <sup>-1</sup> . (b) Trap density estimated using (3.9) with capacita | ance             |

| calculated with the circuit model in Figure 3.4a.                                                                  | 39               |

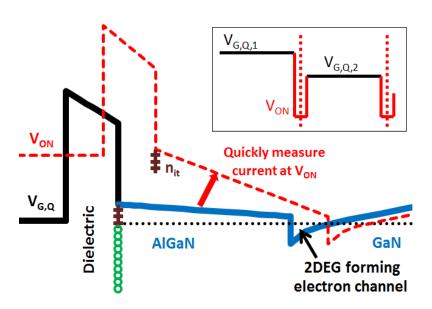

| Figure 3.10: Energy band diagram under the MOS-HFET gate stack (with donor traps) a                                | at ar            |

| applied quiescent gate voltage, $V_{G,Q}$ , with an interface charge $n_{it}$                                      | 41               |

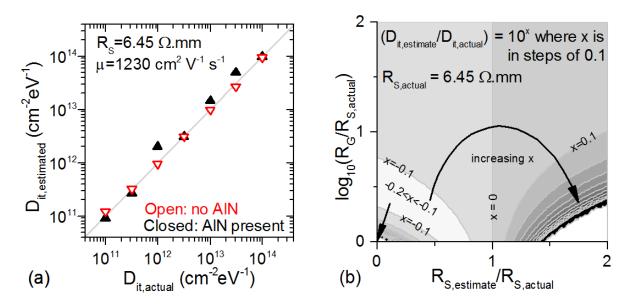

| Figure 3.11: (a) Trap density estimated using TCAD simulations of the pulsed-IV method                             | d for            |

| the barrier with/without the AlN layer. (b) Contour plot of error in estimated                                     | d D <sub>i</sub> |

| as a function of the channel resistance, R <sub>G</sub> , and the estimate of the device se                        | eries            |

| resistance, R <sub>S</sub> .                                                                                       | 42               |

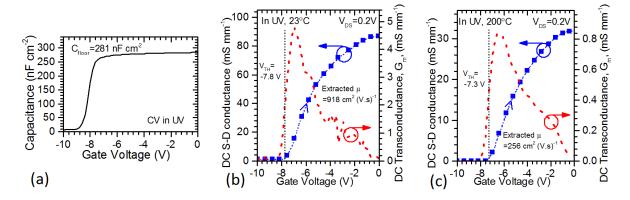

| Figure 3.12: (a) CV measured from 0V to -10V at 1 MHz under UV; (b) GV measure                                     | ed a             |

| room temperature and 200°C with a drain voltage of 0.2V.                                                           | 44               |

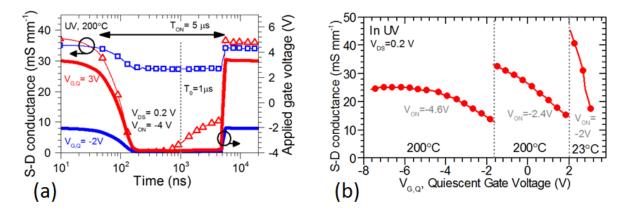

| Figure 3.13: (a) Two transient pulse measurements, under UV, at quiescent gate voltage                             | es of            |

| $3V$ and $-2V$ and a fixed $V_{ON}$ (for time $T_{ON}$ ). (b) S-D conductance measured                             | at 1             |

| $\mu s$ into the measurement pulse at $V_{ON}$ over a quiescent gate voltage, $V_{G,Q}$ , sv                       | veep             |

| with a hold time of 1 s.                                                                                           | 46               |

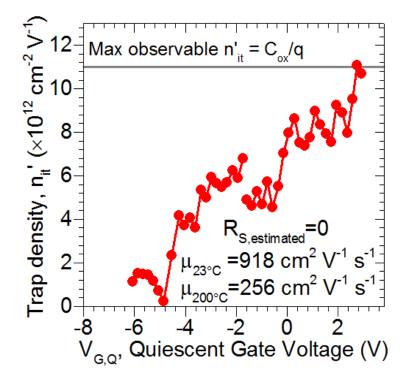

| Figure 3.14: Trap density extracted using (3.12) from the S-D conductance values measured                          | urec             |

| in Figure 3.13b.                                                                                                   | 46               |

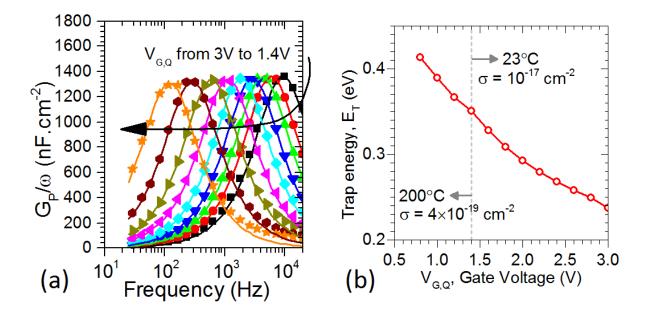

| Figure 3.15: (a) Extracted $GP\omega$ curves and curve-fits for different applied quiescent                        | gate             |

| voltages at 23°C; (b) Trap depth extracted using the peak position of                                              | the              |

| conductance curves                                                                                                 | 47               |

| Figure 3.16: Plot of the constructed trap depth and the rate of band bending curves                                | ovei             |

| different gate voltages.                                                                                           | 48               |

| Figure 3.17: (a) Trap density experimentally estimated using a combination of pulsed-IV                            | and              |

| conductance methods vs. trap depth. (b) Plot of the estimated rate of b                                            | oanc             |

| bending vs. estimated trap density.                                                                                | 48               |

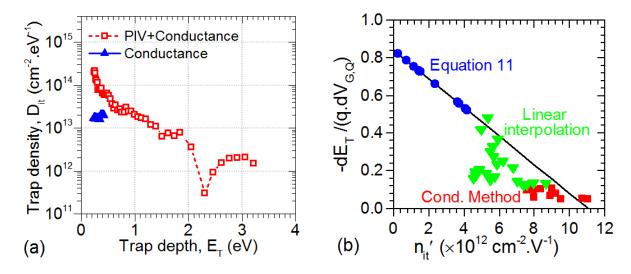

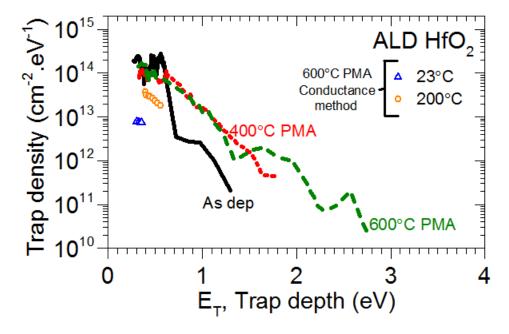

| Figure 4.1: Lines show the interface trap density detected at the ALD HfO <sub>2</sub> /AlGaN inter                | face             |

| using pulsed-IV method for different anneal conditions                                                             | 53               |

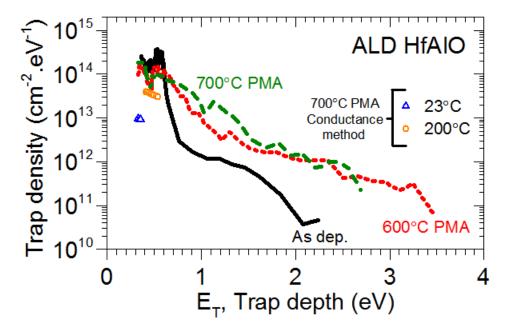

| Figure 4.2: | Lines show the interface trap density detected at the ALD HfAlO/AlGaN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|             | interface using pulsed-IV method for different anneal conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

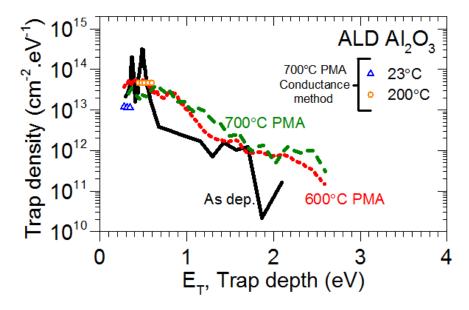

| Figure 4.3: | Lines show the interface trap density detected at the ALD Al <sub>2</sub> O <sub>3</sub> /AlGaN interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|             | using pulsed-IV method for different anneal conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

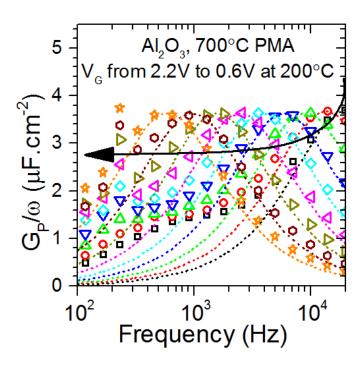

| Figure 4.4: | Conductance curves obtained at 200°C with the MOSHFET having ALD Al <sub>2</sub> O <sub>5</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | gate dielectric after a 700°C PMA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

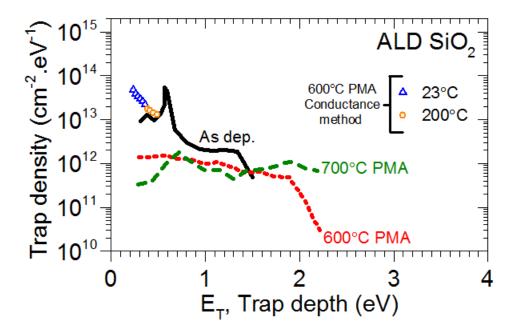

| Figure 4.5: | Lines show the interface trap density detected at the ALD SiO <sub>2</sub> /AlGaN interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | using pulsed-IV method for different anneal conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

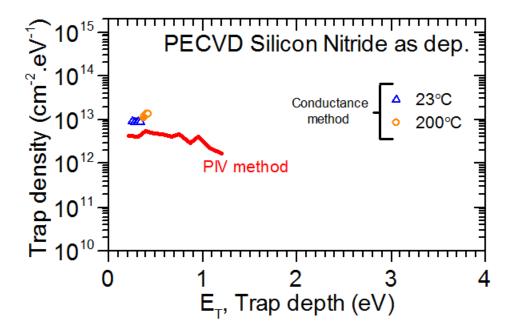

| Figure 4.6  | : Lines show the interface trap density detected at the PECVD silicon                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | nitride/AlGaN interface using pulsed-IV method for the as-deposited condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|             | 58                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

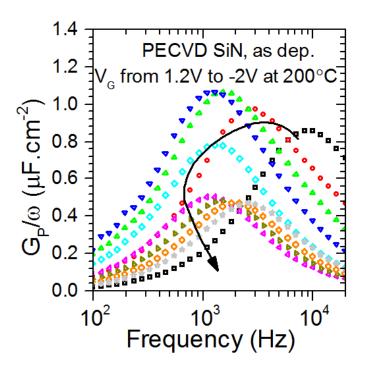

| Figure 4.7: | Conductance curves obtained at 200°C with the MOSHFET having PECVE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | silicon nitride gate dielectric in the as-deposited state                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

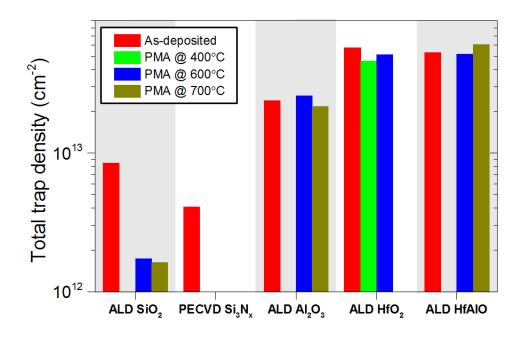

| Figure 4.8: | Bar graph showing the minimum total measured density of traps for different                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|             | dielectrics and annealing conditions from Table 4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

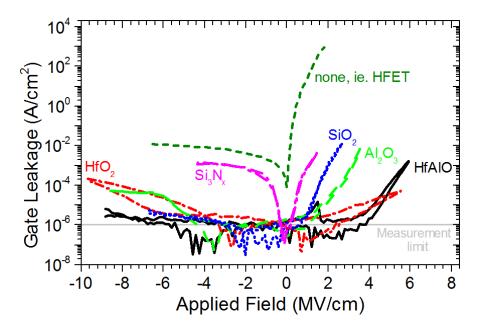

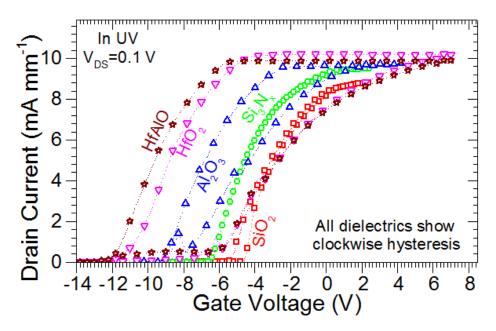

| Figure 5.1: | Best case gate leakage curves measured for different dielectrics in Table 4.1 with                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | identical EOTs. 62                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

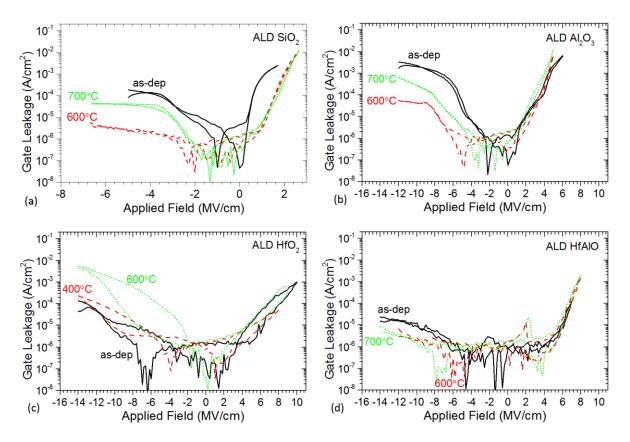

| Figure 5.2: | Gate leakage (I <sub>G</sub> -V <sub>G</sub> ) measured for the MOSHFETs with ALD dielectrics, before                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | and after anneals as described in Table 4.1: (a) $SiO_2$ ; (b) $Al_2O_3$ ; (c) $HfO_2$ ; and (d)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

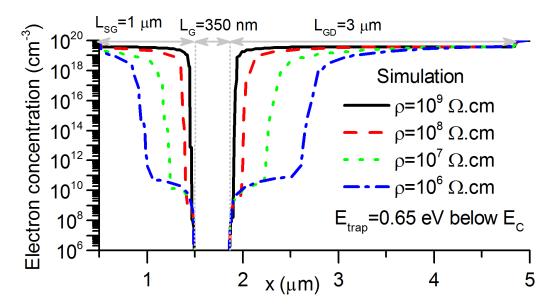

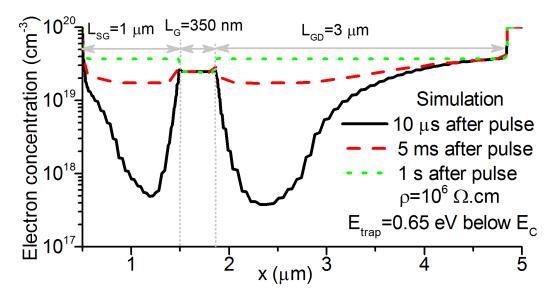

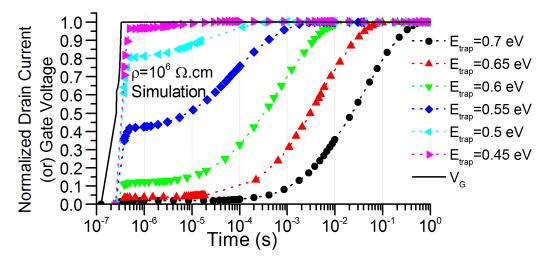

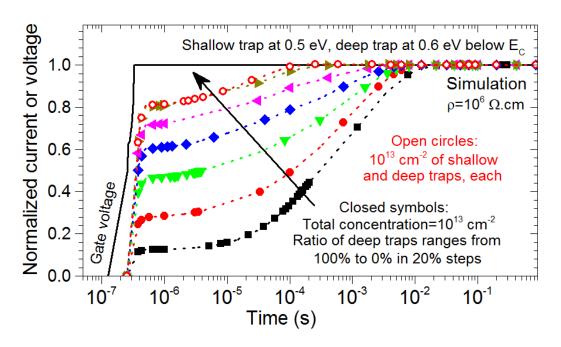

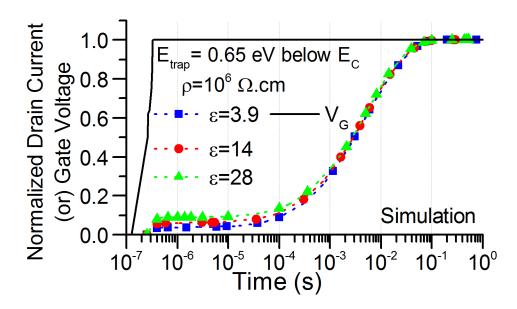

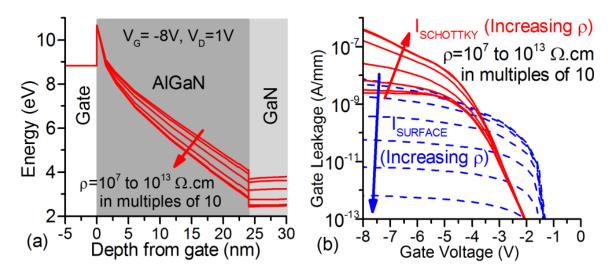

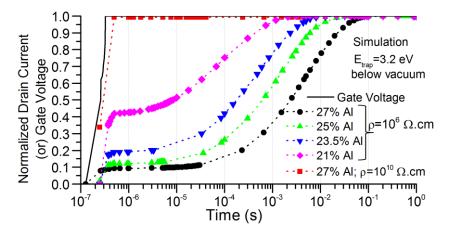

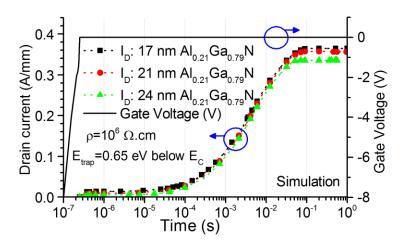

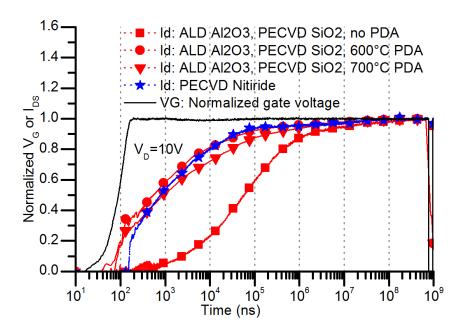

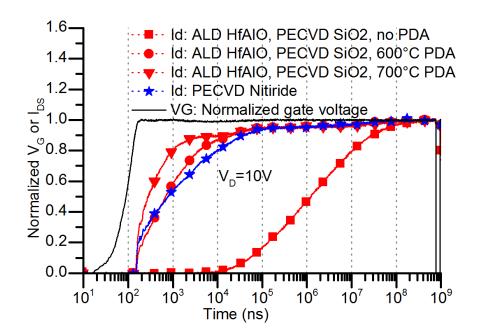

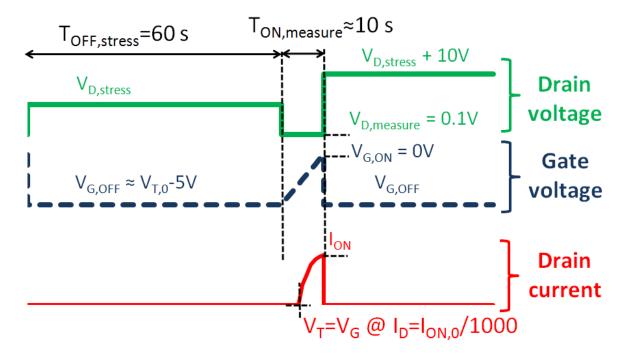

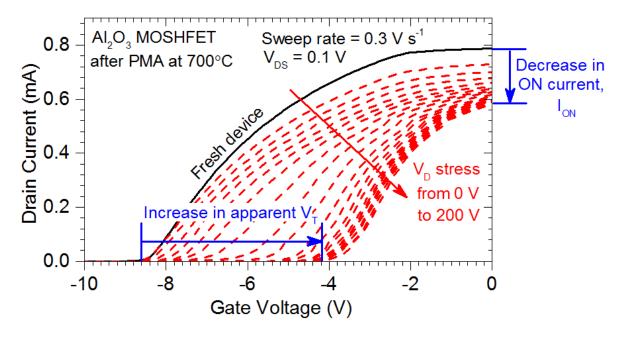

|             | HfAIO63                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |