#### **Abstract**

**Lin, Yanxia.** Advanced Gate Stacks for Strained Silicon Devices (under the direction of Dr. Veena Misra and Dr. Mehmet C. Öztürk).

Due to the mobility enhancement provided by strained Si for both electrons and holes, as well as the scaling requirement and potential issues of polysilicon gate electrodes, alternative gate stacks are being pursued for strained Si devices, which warrant investigation for better understanding on the integration of high-κ dielectrics and metal gate electrodes. Mobility enhancement of strained Si devices has been reported even with ultra-thin SiO<sub>2</sub>. However, additional scattering mechanisms related with high-κ dielectrics and strained Si may result in mobility degradation, which requires a fundamental study. Furthermore, impacts of integration of metal gate electrodes with strained Si channels are not fully understood.

In this work, an investigation of the degradation of electrical properties of several candidate metal gate electrodes on high  $\kappa$  dielectrics on strained Si was performed and compared with that of bulk Si samples. This work consists of three parts. Strained Si layers were grown on relaxed SiGe virtual substrates by ultrahigh vacuum rapid thermal chemical vapor deposition (UHV/RTCVD). High- $\kappa$  dielectrics and metal gates were formed by physical vapor deposition (PVD) methods. The first part of the study focused on the optimization of experimental conditions and the investigation of results from material analysis. The second part of this study compared electrical data from MOS capacitors fabricated with metal gate electrodes on strained Si with SiO<sub>2</sub> as the gate dielectric with that of HfO<sub>2</sub>. Different strained Si

thickness and different Ge concentration in the virtual substrate were employed to study the effects of strain and Ge out-diffusion on electrical properties. Results from strained Si MOSFETs on SiO<sub>2</sub> or HfO<sub>2</sub> with TaN gate electrodes achieved by standard and advanced electrical characterization, including mobility measurement, two and three level charge pumping methods, were analyzed in the last part. It was found that electrical properties degraded as the strained silicon thickness decreased, which was attributed to the presence of Ge in the strained Si layer, and more degradation was observed with SiO<sub>2</sub> which may be due to Si consumption during oxidation. This trend of increasing degradation with decreasing strained silicon thickness did not change after rapid thermal annealing. Metal gate electrodes were found to exhibit as good performance on strained Si as on bulk Si. Strain does not lead to any degradation of the high-k/strained Si interface. Ge diffusion is the dominant cause of the Dit increase, which explains that samples with thinner strained Si films show less device performance enhancement. Less degradation with HfO<sub>2</sub> samples was observed due to the low temperature formation process of high-k dielectrics. The mechanisms responsible for mobility degradation in strained Si devices with advanced gate stacks were discussed.

## ADVANCED GATE STACKS FOR STRAINED SILICON DEVICES

by

## Yanxia Lin

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

**ELECTRICAL AND COMPUTER ENGINEERING**

| _   |        |        |   |

|-----|--------|--------|---|

| บา  | $\sim$ | $\sim$ | h |

| Ral |        | u      |   |

|     | •      | .7     |   |

2005

APPROVED BY:

| Dr. Veena Misra                 | Dr. Mehmet C. Öztürk               |

|---------------------------------|------------------------------------|

| Chair of the advisory committee | Co-Chair of the advisory committee |

| Dr. C.M. Osburn                 | Dr. G.N. Parsons                   |

# To the memory of my dear father

Thiying Lin

(1932 ~ 2002)

My mother

Wenying Weng

My sister

Yanli Lin

My niece

Yujing Fang

and

My husband

Tao Onyang

## **Biography**

Yanxia Lin received her Bachelor degree in Materials Science and Engineering from Tsinghua University in July 1997, and her M.S. degree in Materials Science from the Institute of Semiconductors of Chinese Academy of Sciences in July 2000, both in Beijing, China. Upon completion of her studies in China, she was admitted to the PhD program in the Department of Electrical and Computer Engineering at North Carolina State University. She started her doctoral work in the summer of 2001 as a research assistant under the direction of Dr. Mehmet C. Öztürk. One year later she started working on the strained Silicon project under the guidance of Dr. Veena Misra, with Dr. Öztürk as her co-advisor.

Following graduation Yanxia Lin will join Spansion LLC in Austin, Texas.

## Acknowledgements

I would like to express my sincere gratitude to my advisor, Dr. Veena Misra, for providing me the research opportunities, as well as her guidance, support and encouragement throughout the past four years. Without her supervision, I would not be in the stage where I am now. I am also very thankful to Dr. Mehmet C. Öztürk, for all the knowledge that he has taught me on research and life.

I am also honored to have Dr. C. M. Osburn and Dr. G. R. Parsons in my committee. I would like to thank them for their interest and encouragement throughout this research.

Many thanks to the AEMP cleanroom staff including Joan O'Sullivan, Harold Morton, Dr. Ginger Yu, Henry Taylor, Myrick Peacock for all of the work they have done in keeping the laboratory running and their kindly help in processing.

I would also like to acknowledge many past and present graduate students including Jing Liu, Hongxiang Mo, Jennifer Yopp, Heather Lazar, Nemanja Pesovic, Bei Chen, Jaehoon Lee, Youseok Suh, Rashmi Jha, Qiliang Li, Guru Mathur, Saurabh Chopra, Sriv Godwa and Yan Du for their help and many joyful discussions.

Finally, I also wish to acknowledge my parents and my sister for their endless love, encouragement and support. I would like to thank my husband, Tao Ouyang, for his patience, understanding and sacrifice which made this degree possible.

## **Table of Contents**

| LIST OF FIGUR | ES                                                                | IX |

|---------------|-------------------------------------------------------------------|----|

| LIST OF TABLE | ES                                                                | XV |

| CHAPTER 1     | INTRODUCTION                                                      |    |

| 1.1 CMOS TI   | ECHNOLOGY SCALING                                                 | 1  |

| 1.2 STRAINEI  | SILICON TECHNOLOGY                                                | 4  |

| 1.2.1         | Why Is Strained Silicon Required for Future CMOS Devices          | 4  |

| 1.2.2         | Biaxial Strained Silicon and Device Applications                  | 8  |

| 1.2.3         | Uniaxial Strained Silicon and Device Applications                 | 12 |

| 1.3 ALTERNA   | TIVE HIGH DIELECTRIC CONSTANT GATE INSULATOR MATERIALS            | 16 |

| 1.3.1         | Why Are High κ Dielectrics Required                               | 16 |

| 1.3.2         | Hafnium Based Dielectrics                                         | 18 |

| 1.3.3         | Additional Problems with High κ Dielectrics                       | 19 |

| 1.4 METAL G   | ATE ELECTRODES                                                    | 20 |

| 1.4.1         | Why Do We Need Metal Gates                                        | 20 |

| 1.4.2         | Current Candidates: Advantages and Problems                       | 21 |

| 1.5 ADVANCE   | ED GATE STACKS ON STRAINED SILICON AND CURRENT CHALLENGES         | 22 |

| 1.5.1         | Strained Silicon with Novel Gate Stacks                           | 22 |

| 1.5.2         | Current issues: Process and Device Design                         | 23 |

| 1.6 OUTLINE   | OF THE DISSERTATION                                               | 24 |

| 1.7 Reference | CES                                                               | 26 |

| CHAPTER 2     | FABRICATION OF STRAINED SILICON DEVICES INCORPORATING             |    |

| ALTERNATI     | VE GATE STACKS                                                    |    |

| 2.1 EPITAXY   | OF SI <sub>1-x</sub> Ge <sub>x</sub> and Strained Si Layer        | 33 |

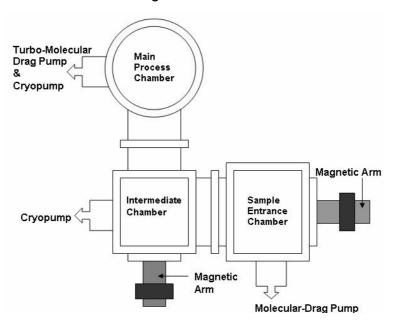

| 2.1.1         | UHV-RTCVD System                                                  | 33 |

| 2.1.2         | Surface Preparation Prior to Six "Ge," and Strained Si Deposition | 35 |

| 2.1.3        | Selective Deposition of Boron Doped Si and Si <sub>1-x</sub> Ge <sub>x</sub>              | 37   |

|--------------|-------------------------------------------------------------------------------------------|------|

| 2.2 НіGH к I | DIELECTRIC AND METAL GATE ELECTRODE DEPOSITION                                            | 38   |

| 2.2.1        | UHV-Sputtering System                                                                     | 38   |

| 2.2.2        | High-κ Dielectric Formation                                                               | 40   |

| 2.2.3        | Metal Gate Electrodes used in this work                                                   | 41   |

| 2.3 PROCESS  | FLOW OF STRAINED SI MOSFETS.                                                              | 42   |

| 2.4 Referen  | ICES                                                                                      | 44   |

| CHAPTER 3    | MATERIAL ANALYSIS AND ELECTRICAL CHARACTERIZATION                                         |      |

| 3.1 MATERIA  | AL ANALYSIS                                                                               | 46   |

| 3.2 Electri  | CAL ANALYSIS                                                                              | 49   |

| 3.2.1        | Capacitance-Voltage Measurement                                                           | 50   |

| 3.2.2        | Interface Trap Density Measurement                                                        | 52   |

| 3.2.3        | Current-Voltage Measurement                                                               | 57   |

| 3.2.4        | Mobility Measurement                                                                      | 61   |

|              | 3.2.4.1 Split C-V Method                                                                  | 62   |

|              | 3.2.4.2 Corrections of Mobility Extraction                                                | 65   |

| 3.2.5        | Charge Pumping                                                                            | 68   |

|              | 3.2.5.1 Two Level Charge Pumping                                                          | 68   |

|              | 3.2.5.2 Three Level Charge Pumping                                                        | 71   |

| 3.3 Referen  | ICES                                                                                      | 74   |

| CHAPTER 4    | MATERIALS ANALYSIS AND ELECTRICAL CHARACTERIZATION O                                      | )F   |

| STRAINED S   | SI FILMS AND HIGH-K DIELECTRICS                                                           |      |

| 4.1 Propert  | TIES OF SI <sub>1-x</sub> Ge <sub>x</sub> and Strained Si Films Used in this work         | 76   |

| 4.1.1        | Selectivity of Deposition                                                                 | 76   |

| 4.2 PROPERT  | TIES OF HIGH-K DIELECTRICS: HFO <sub>2</sub>                                              | 86   |

| 4.2.1        | Electrical Characteristics of HfO <sub>2</sub> Metal-Oxide-Semiconductor (MOS) Capacitors | 87   |

| 4.2.2        | X-ray Photoelectron Spectroscopy (XPS) and Transmission Electron Microscopy (TEM          | Л)90 |

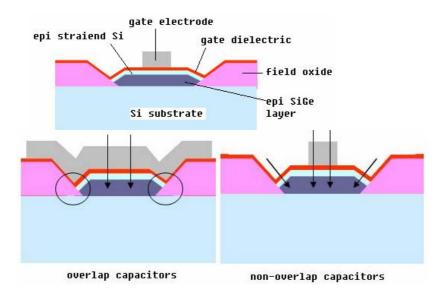

| 4.3      | EFFECTS C | F FACETS ON ELECTRICAL PROPERTIES                                                             | 96  |

|----------|-----------|-----------------------------------------------------------------------------------------------|-----|

|          | 4.3.1     | Overlap and Non-overlap Capacitors                                                            | 97  |

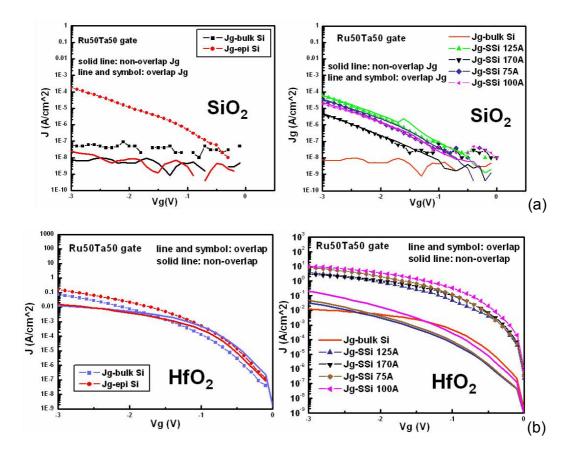

|          | 4.3.2     | I-V Measurement of Overlap and Non-overlap Capacitors                                         | 98  |

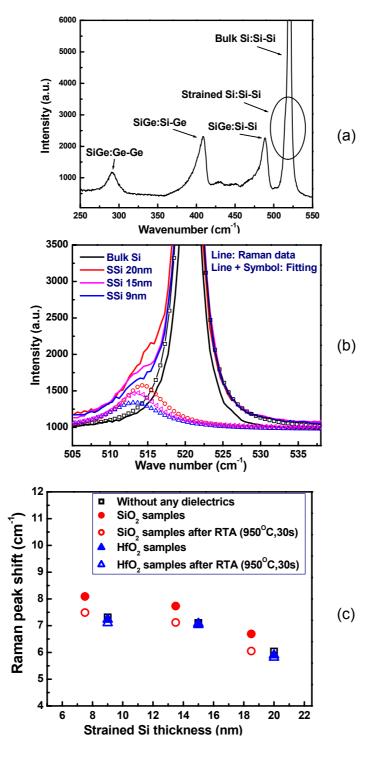

| 4.4      | STRAIN A  | NALYSIS BY RAMAN SPECTROSCOPY                                                                 | 100 |

| 4.5      | REFERENC  | DES                                                                                           | 103 |

| СНА      | PTER 5    | MATERIALS ANALYSIS AND ELECTRICAL CHARACTERIZATION OF                                         | =   |

|          |           | I METAL-OXIDE-SEMICONDUCTOR (MOS) CAPACITORS                                                  |     |

| <b>-</b> |           | THE TAE ONBE GEIMOON BOOTON (MOO) OAT AOTTONO                                                 |     |

| 5.1      | ELECTRICA | AL CHARACTERIZATION OF STRAINED SI MOS CAPACITORS                                             | 106 |

|          | 5.1.1     | Electrical properties of Samples after Forming Gas Anneal (FGA)                               | 107 |

|          | 5.1.2     | Electrical properties of Samples after Rapid Thermal Anneal (RTA)                             | 110 |

| 5.2      | POSSIBLE  | MECHANISMS OF ELECTRICAL PROPERTY DEGRADATION                                                 | 112 |

| 5.3      | SUMMARY   | ,                                                                                             | 119 |

| 5.4      | REFERENC  | TES                                                                                           | 121 |

| 5.5      | IMPACT OF | F $ m Ge$ on integration of $ m HfO_2$ and metal gate electrodes on strained $ m Si$ channels | 122 |

| СПУ      | DTED 6    | ELECTRICAL CHARACTERIZATION OF STRAINED SI MOSFETS                                            |     |

| СПА      | PIERO     | ELECTRICAL CHARACTERIZATION OF STRAINED ST MOSFETS                                            |     |

| 6.1      | STRAINED  | Si MOSFETS with $\mathrm{SiO}_2$ Gate Dielectric and Polysilicon or TaN Gate Electrode        | S   |

|          |           |                                                                                               | 138 |

|          | 6.1.1     | Basic Device Characteristics: C-V and I-V                                                     | 139 |

|          | 6.1.2     | Mobility Extraction                                                                           | 141 |

| 6.2      | STRAINED  | SI MOSFETS WITH TAN GATE: SIO <sub>2</sub> OR HFO <sub>2</sub>                                | 142 |

|          | 6.2.1     | Basic Device Characteristics: C-V and I-V                                                     | 143 |

|          | 6.2.2     | Mobility Extraction                                                                           | 146 |

|          | 6.2.3     | Interface and Bulk Traps                                                                      | 148 |

| 6.3      | MOBILITY  | DEGRADATION MECHANISMS IN STRAINED SI MOSFETS WITH TAN GATE ELECTRODES                        | 154 |

|          | 6.3.1     | Mobility Correction for Interface Traps                                                       | 154 |

|          | 6.3.2     | Mobility Degradation Related to High-κ Dielectrics                                            | 159 |

|          | 6.3.3     | Mobility of Strained Si MOSFETs at Higher Temperatures                                        |     |

|          |           |                                                                                               |     |

|     | 6.3.4    | The Impact of Ge on Mobility Degradation                   | 163 |

|-----|----------|------------------------------------------------------------|-----|

|     | 6.3.5    | Understanding Scattering Mechanisms in strained Si devices | 166 |

| 6.4 | SUMMARY  | <i>(</i>                                                   | 170 |

| 6.5 | REFERENC | CES                                                        | 172 |

| СНА | PTER 7   | SUMMARY AND FUTURE WORK                                    |     |

|     |          |                                                            |     |

| 7.1 | Conclus  | IONS                                                       | 175 |

| 7.2 | FUTURE V | VORK                                                       | 177 |

## **List of Figures**

| Figure 1-1 | Schematic representation of the strain induced conduction band splitting in silicon                           |

|------------|---------------------------------------------------------------------------------------------------------------|

|            | 5                                                                                                             |

| Figure 1-2 | Energy alignment of the Si conduction band with and without the tensile strain in (a)                         |

|            | bulk and (b) inversion layer, respectively6                                                                   |

| Figure 1-3 | Simplified hole valence band structure for longitudinal in plane direction (a)                                |

|            | unstrained and (b) strained silicon                                                                           |

| Figure 1-4 | Schematic illustrations of (a) equilibrium lattices and (b) pseudomorphic strained Si                         |

|            | on relaxed SiGe (c) band alignments between strained Si and the relaxed SiGe                                  |

|            | virtual substrate9                                                                                            |

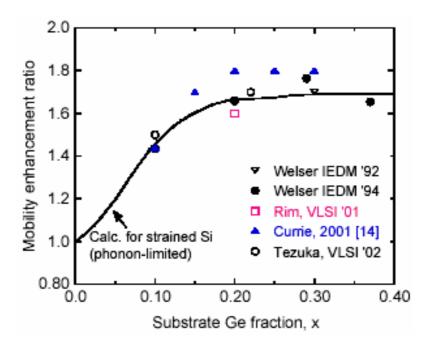

| Figure 1-5 | Measured (symbols) effective mobility enhancement ratios, r, compared to                                      |

|            | calculations for the phonon limited MOS mobility (solid line) for strained Si n-                              |

|            | MOSFETs11                                                                                                     |

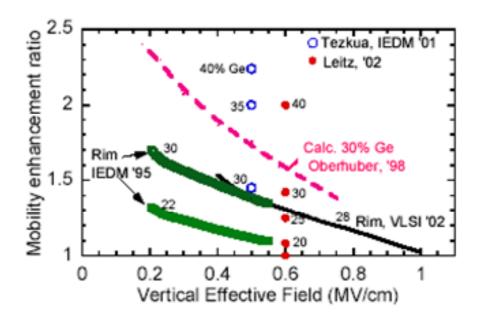

| Figure 1-6 | Comparison of hole mobility enhancement ratios in strained Si p-MOSFETs as a                                  |

|            | function of vertical effective field, $E_{eff}$ . The numbers beside the data are the substrate               |

|            | Ge percent                                                                                                    |

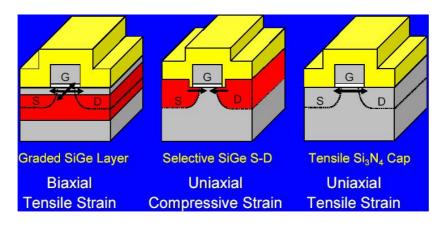

| Figure 1-7 | Schematic showing different types of strain induced in the silicon channel                                    |

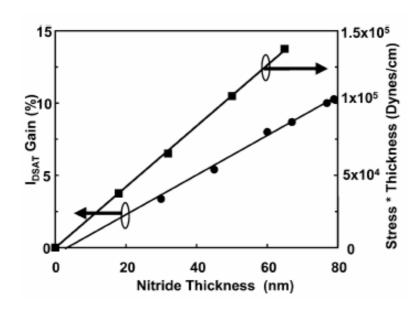

| Figure 1-8 | Electron saturated drive current improvement verses nitride thickness                                         |

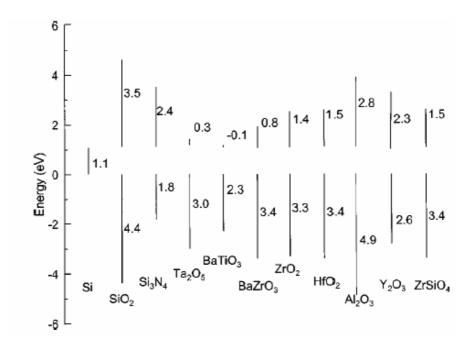

| Figure 1-9 | Band offset calculations for a number of potential high-κ gate dielectric materials18                         |

| Figure 2-1 | A schematic illustration of UHV-RTCVD system used in this work                                                |

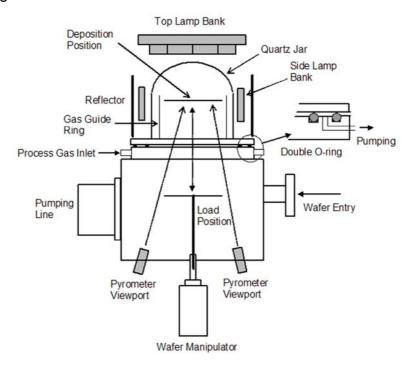

| Figure 2-2 | The main process chamber (MPC) of the UHV-RTCVD system consists of a quartz                                   |

|            | bell jar, a top lamp bank, and a side lamp bank35                                                             |

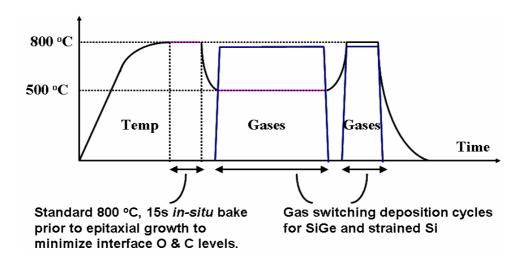

| Figure 2-3 | A typical deposition sequence used in Si <sub>1-x</sub> Ge <sub>x</sub> and Si epitaxy                        |

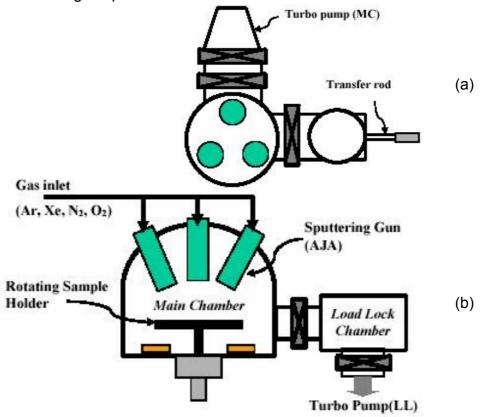

| Figure 2-4 | Schematic of the UHV RF sputtering system: (a) top view; (b) side view39                                      |

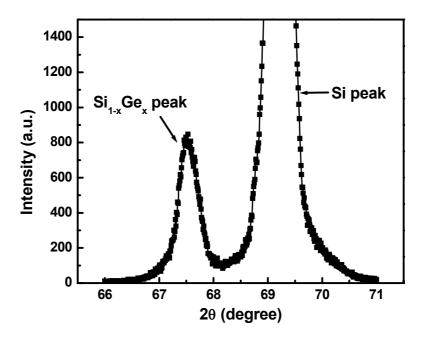

| Figure 3-1 | XRD spectra of 100nm Si <sub>1-x</sub> Ge <sub>x</sub> film deposited on a crystalline bulk silicon substrate |

|            | where x is about 50%47                                                                                        |

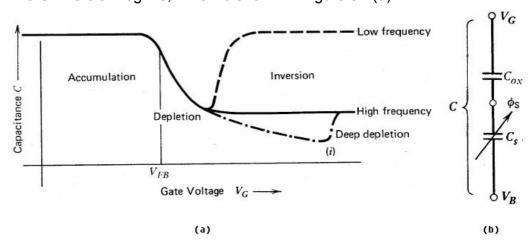

| Figure 3-2 | (a) The C-V characteristic of a MOS capacitor on P-type Si substrate. (b) The                                 |

|            | electrical equivalent circuit of a MOS capacitor50                                                            |

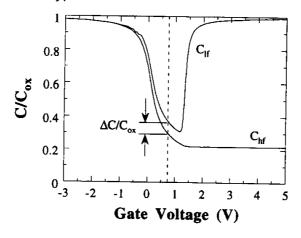

| Figure 3-3  | High and low-frequency C-V curves show the offset $\Delta C/C_{ox}$ due to interface traps53        |

|-------------|-----------------------------------------------------------------------------------------------------|

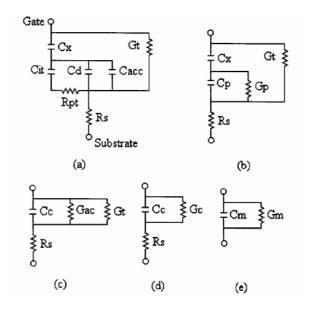

| Figure 3-4  | Equivalent circuits for conductance measurements55                                                  |

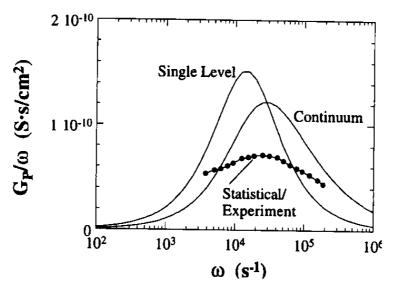

| Figure 3-5  | $G_p/\omega$ versus $\omega$ for a single level, a continuum and experimental data. For all curves: |

|             | $D_{it}$ =1.9×10 <sup>9</sup> cm <sup>-2</sup> eV <sup>-1</sup> , $\tau_{it}$ =7×10 <sup>-5</sup> s |

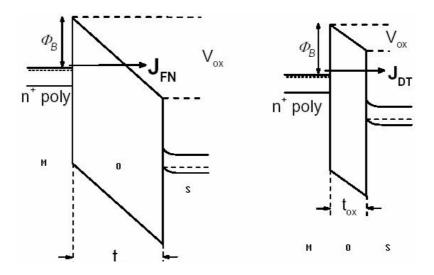

| Figure 3-6  | Energy band diagram description of (a) Fowler-Nordheim injection through a                          |

|             | triangular barrier and (b) direct tunneling through a trapezoidal barrier60                         |

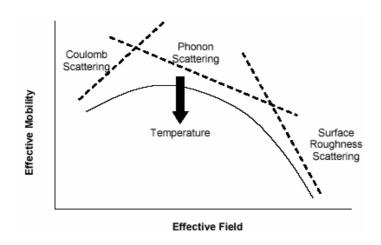

| Figure 3-7  | Plot of overall mobility versus effective field limited by various scattering mechanisms.           |

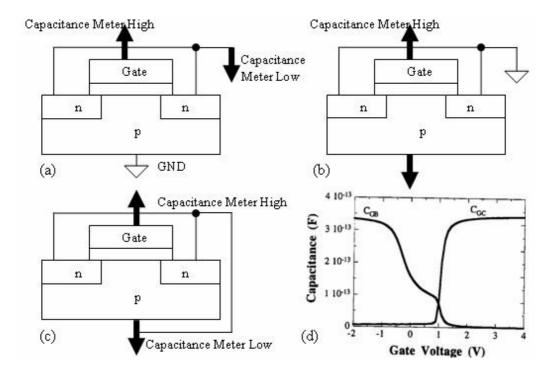

| Figure 3-8  | Schematics of experimental setup to measure (a) gate to channel capacitance for                     |

|             | Split C-V, (b) gate to substrate capacitance, and (c) total gate capacitance; and (d)               |

|             | gate-to-channel and gate-to-substrate capacitance as a function of gate voltage 64                  |

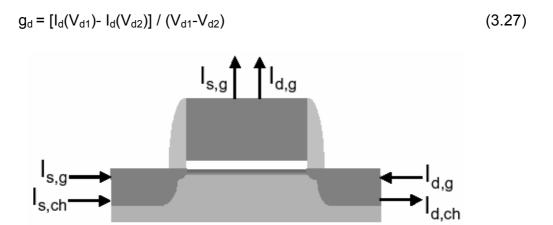

| Figure 3-9  | Schematic of an nMOSFET showing the current components in the $I_d\!\!-\!\!V_g$                     |

|             | measurement67                                                                                       |

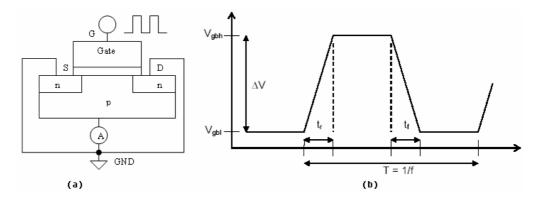

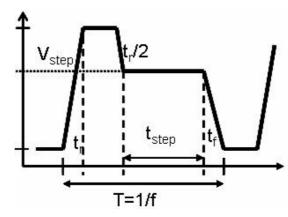

| Figure 3-10 | Schematic of (a) the charge pumping measurement configuration; (b) the square                       |

|             | wave pulse used in two level charge pumping69                                                       |

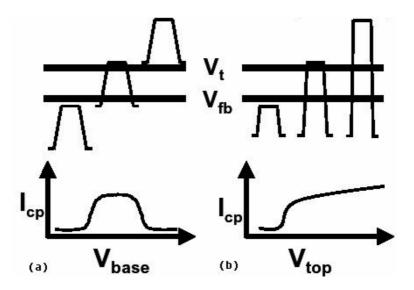

| Figure 3-11 | Schematic of the waveforms and resulting $I_{\text{cp}}$ of (a) the Base Sweep and (b) the          |

|             | Amplitude Sweep of two level charge pumping measurements70                                          |

| Figure 3-12 | Schematic of the waveform used in the three level charge pumping to profile interface               |

|             | traps with energies between E <sub>c</sub> and E <sub>i</sub> 72                                    |

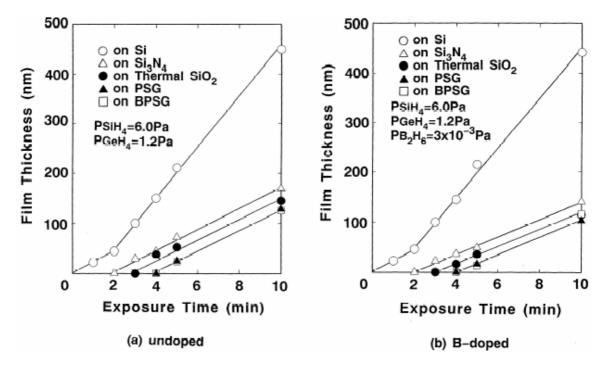

| Figure 4-1  | Incubation time plotted as a function of insulator materials                                        |

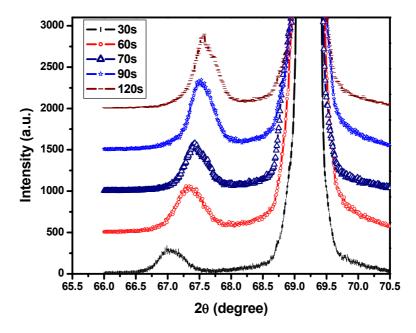

| Figure 4-2  | XRD scans for the deposited films with same gas flow but different thickness.                       |

|             | Deposition parameters are listed in Table 4-181                                                     |

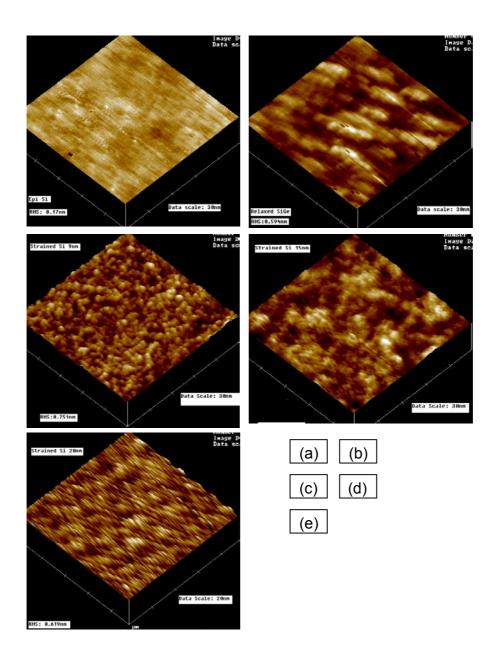

| Figure 4-3  | AFM surface scans of deposited films: (a) epi Si: RMS ~0.17 nm (Z scale 30 nm); (b)                 |

|             | $Si_{1-x}Ge_x$ : RMS ~0.59 nm (Z scale 30 nm); (c) strained Si (9 nm): RMS ~0.75 nm (Z              |

|             | scale 30 nm); (d) strained Si (15 nm): RMS ~0.60 nm (Z scale 30 nm); (e) strained Si                |

|             | (20 nm): RMS ~0.62 nm (Z scale 20 nm)                                                               |

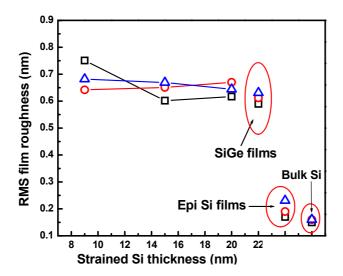

| Figure 4-4  | RMS roughness of deposited films plotted as a function of strained Si thickness 86                  |

| Figure 4-5  | C-V and I-V characteristics of four HfO <sub>2</sub> samples whose process conditions are listed            |

|-------------|-------------------------------------------------------------------------------------------------------------|

|             | in Table 4-3: (a) C-V data; (b) $J_{\rm g}$ plotted as a function of voltage across the oxide               |

|             | $(V_{ox})$ ; (c) $J_g$ of $SiO_2$ from reference; (d) deviation of $J_g$ observed from the I-V data of      |

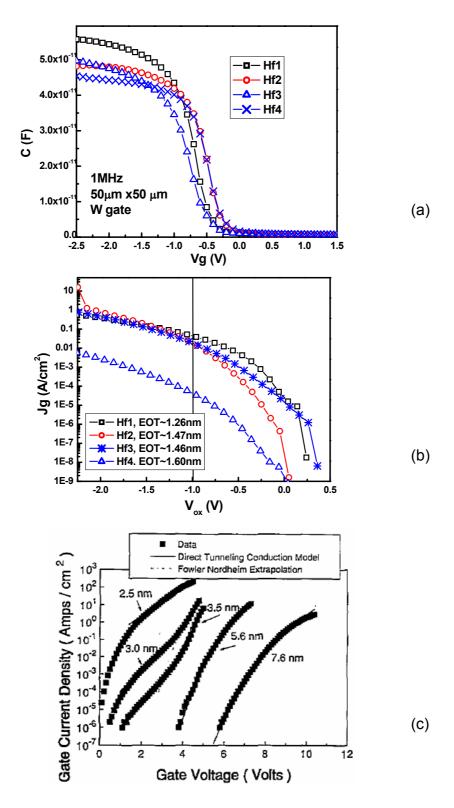

|             | sample Hf390                                                                                                |

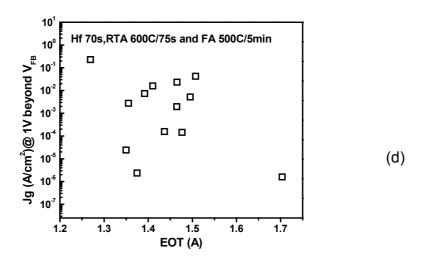

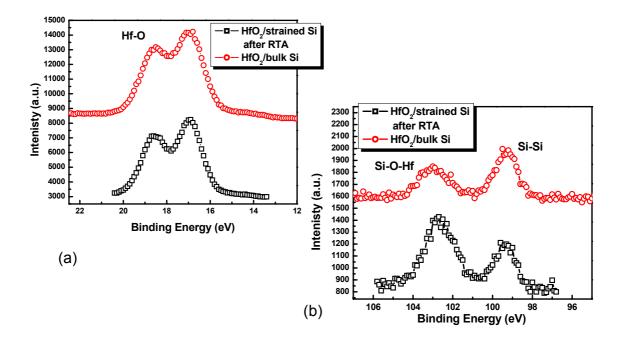

| Figure 4-6  | The XPS spectra of (a) Hf 4f and (b) Si 2p core-levels of two HfO <sub>2</sub> /Si samples 92               |

| Figure 4-7  | The XPS spectra of (a) Hf 4f and (b) Si 2p core-levels of a RTA HfO <sub>2</sub> /strained Si               |

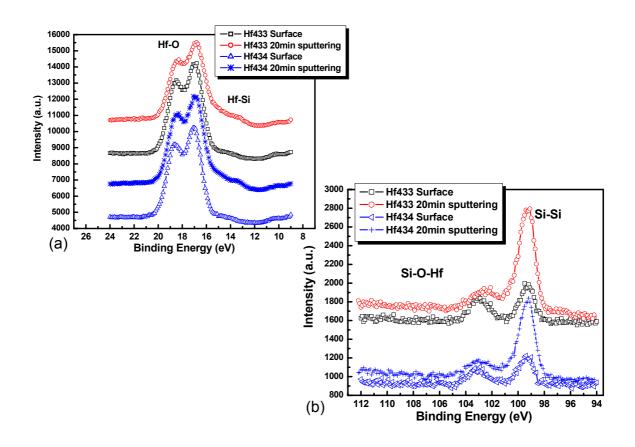

|             | sample compared to the HfO <sub>2</sub> /bulk Si system93                                                   |

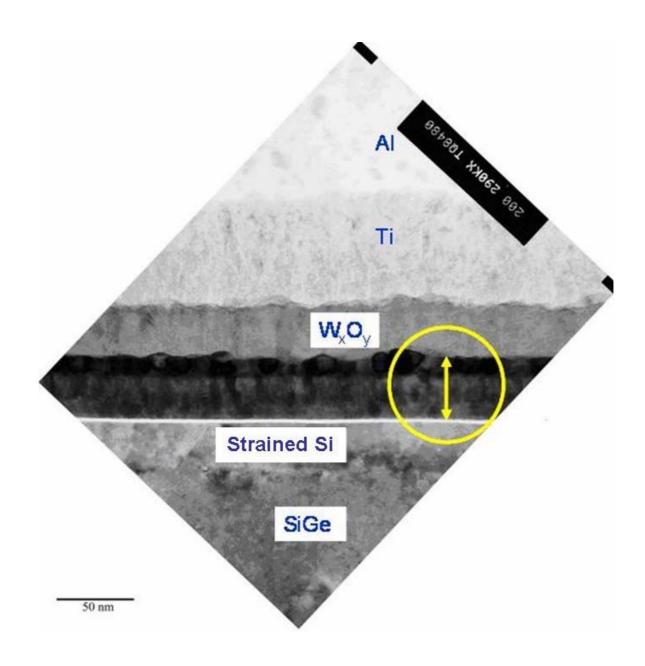

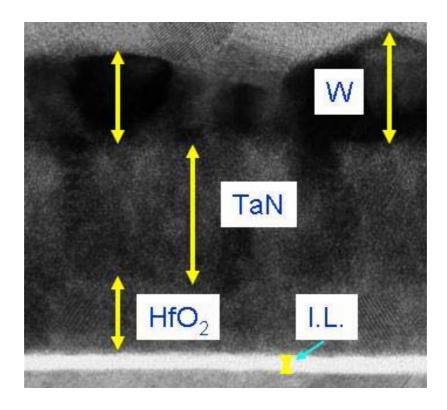

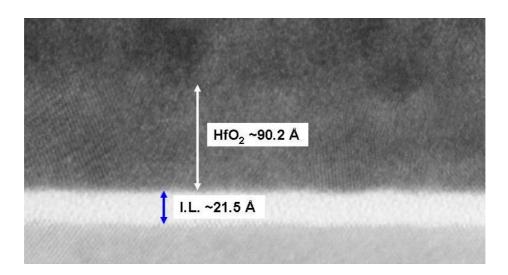

| Figure 4-8  | A TEM image of a strained Si sample with high $\kappa$ and metal gate electrode stacks. All                 |

|             | layers were labeled in (a) and (b) while details of HfO2 and the interfacial layer were                     |

|             | shown in (c)95                                                                                              |

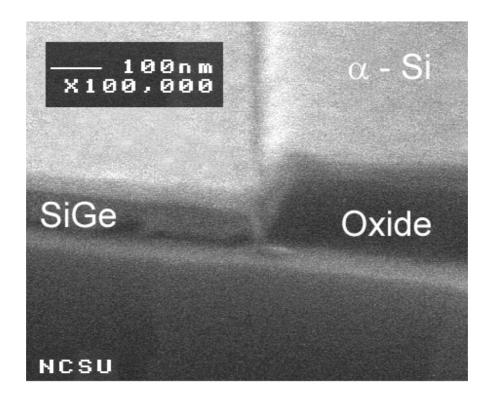

| Figure 4-9  | A SEM image of selectively deposited SiGe layer confined in the active area,                                |

|             | achieved by S. Chopra working in the same group as the author in NCSU97                                     |

| Figure 4-10 | Schematic illustration of cross-sections of overlap and non-overlap capacitors98                            |

| Figure 4-11 | Leakage current densities of overlap and non-overlap capacitors with (a) SiO <sub>2</sub> and (b)           |

|             | HfO <sub>2</sub> as gate dielectrics99                                                                      |

| Figure 4-12 | Raman spectra of strained Si samples with different thicknesses: (a) a typical Raman                        |

|             | spectrum of a strained Si sample; (b) different strain level was achieved by varying                        |

|             | strained Si thickness; (c) Raman peak shifts plotted as a function of strained S                            |

|             | thickness                                                                                                   |

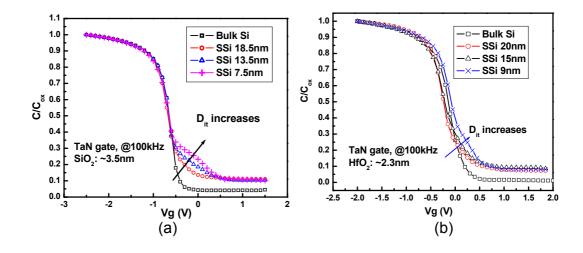

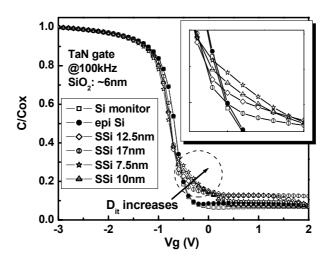

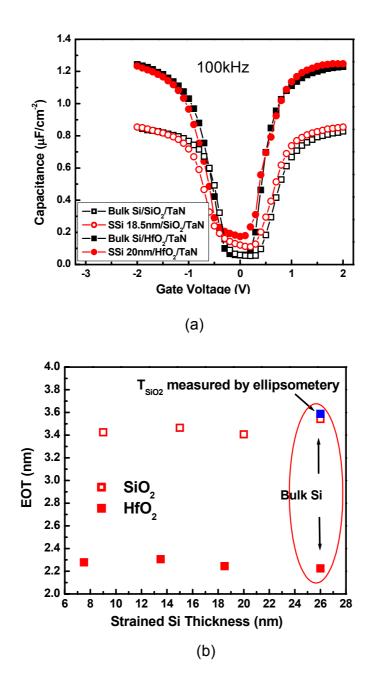

| Figure 5-1  | C-V curves from MOS capacitors with SiO <sub>2</sub> and HfO <sub>2</sub> gate dielectrics and TaN gate     |

|             | electrodes. The measured area is 50μm by 50μm107                                                            |

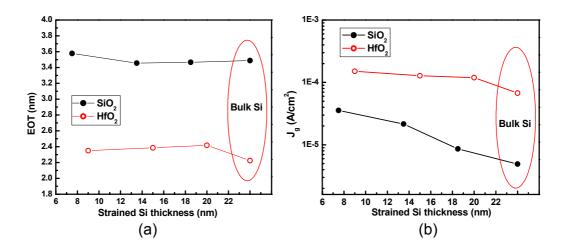

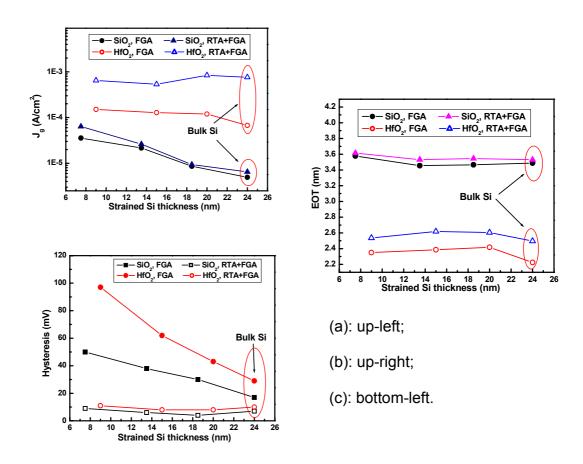

| Figure 5-2  | (a) Equivalent oxide thickness and (b) leakage current density of SiO <sub>2</sub> and HfO <sub>2</sub>     |

|             | samples are plotted vs. strained Si thickness. The gate electrodes are TaN 108                              |

| Figure 5-3  | Hysteresis of SiO <sub>2</sub> and HfO <sub>2</sub> samples are plotted vs. strained Si thickness, with TaN |

|             | as the gate electrodes                                                                                      |

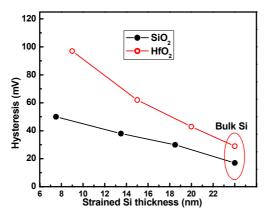

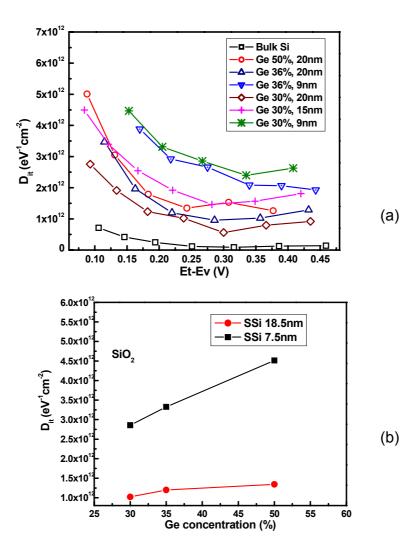

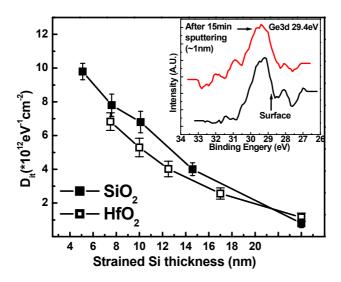

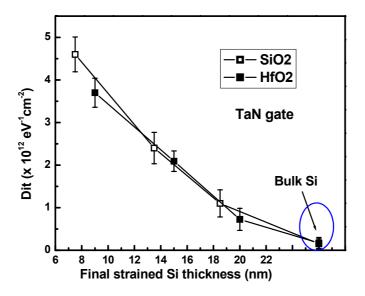

| Figure 5-4  | The density of interface traps (Dit) plotted as a function of (a) the trap energy; (b)                      |

|             | strained Si thickness110                                                                                    |

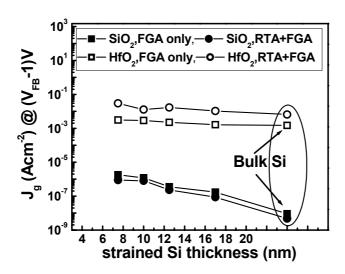

| Figure 5-5  | Electrical parameters of TaN gate MOS capacitors after RTA plotted vs. strained S                       |

|-------------|---------------------------------------------------------------------------------------------------------|

|             | thickness: (a) leakage current density at 1V beyond $V_{FB}$ ; (b) EOT; (c) hysteresis 11               |

| Figure 5-6  | Interface trap density (D <sub>it</sub> ) after RTA is plotted as a function of strained Si thickness   |

|             | The gate electrode is TaN11                                                                             |

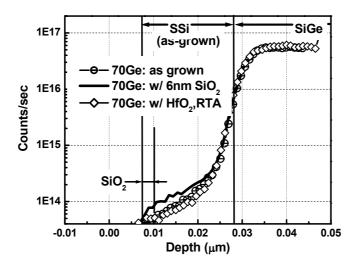

| Figure 5-7  | Ge profiles from SIMS show the effect of high temperature process on Ge out                             |

|             | diffusion. Samples have 20nm strained Si layer11                                                        |

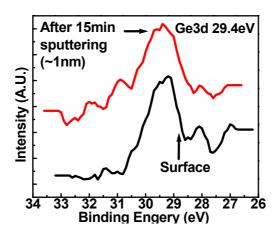

| Figure 5-8  | XPS spectrum of Ge 3d core level of a 9nm strained Si/ 3.5nm SiO <sub>2</sub> sample with th            |

|             | oxide removed11                                                                                         |

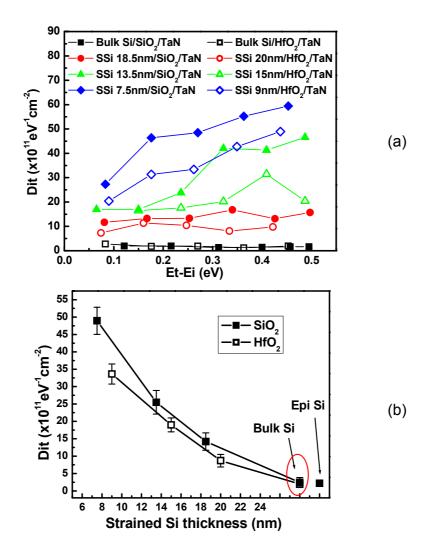

| Figure 5-9  | The density of interface traps (D <sub>it</sub> ) plotted as a function of (a) the trap energy; (b) G   |

|             | concentration with varying strained Si thickness. TaN is used as the gate electrode                     |

|             | 11                                                                                                      |

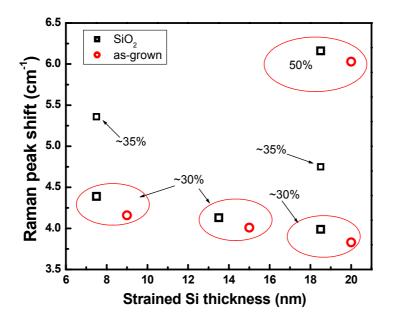

| Figure 5-10 | Raman peak shifts plotted vs. strained Si thickness with varying Ge content in th                       |

|             | virtual substrate11                                                                                     |

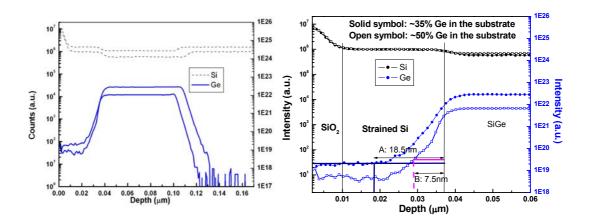

| Figure 5-11 | SIMS profiles of Si and Ge of two strained Si samples with different Ge content in the                  |

|             | SiGe buffer layer. It can be seen that more Ge out-diffusion into the strained S                        |

|             | channel would be expected in sample B than in sample A11                                                |

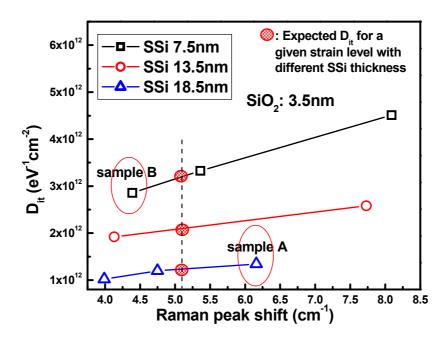

| Figure 5-12 | Dit plotted as a function of Raman peak shift with varying Ge content in the SiG                        |

|             | virtual substrate. Sample A and B refer to the conditions listed in Figure 5-11 11                      |

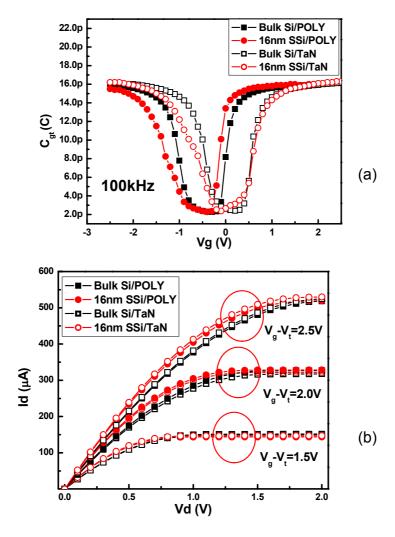

| Figure 6-1  | Basic electrical characteristics of bulk Si and strained Si (16nm) MOSFETs wit                          |

|             | POLY and TaN gate electrodes: (a) C-V curves; (b) drain currents14                                      |

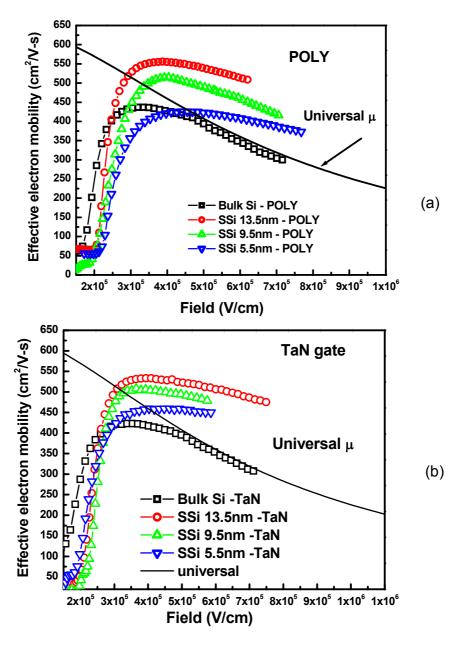

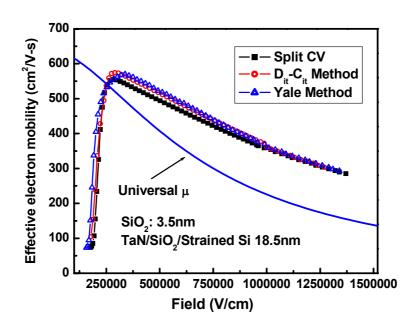

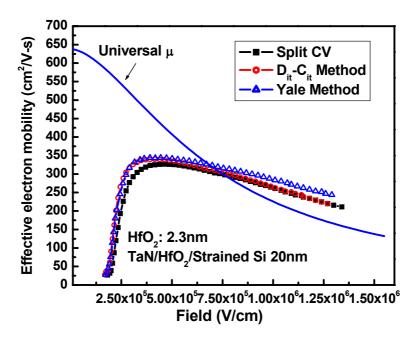

| Figure 6-2  | Mobilities of polysilicon and TaN metal gates on SiO <sub>2</sub> dielectrics extracted by Split C      |

|             | V analysis                                                                                              |

| Figure 6-3  | (a) C-V curves of TaN nMOSFETs on bulk Si or 20nm strained Si with SiO <sub>2</sub> or HfO <sub>2</sub> |

|             | (b) EOT values plotted as a function of strained Si thickness                                           |

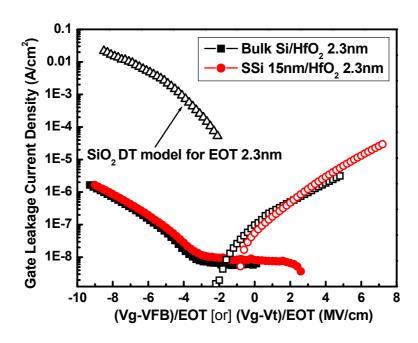

| Figure 6-4  | Comparison of gate leakage current for strained Si and bulk Si nFETs with SiO <sub>2</sub> an           |

|             | HfO <sub>2</sub> 14                                                                                     |

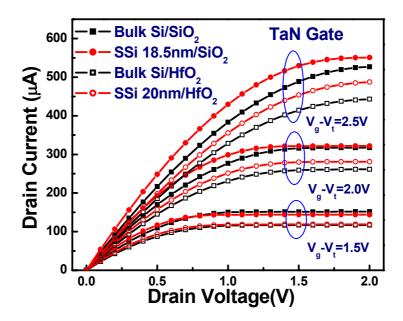

| Figure 6-5  | Drain currents of TaN gate MOSFETs on SiO <sub>2</sub> and HfO <sub>2</sub> 14                          |

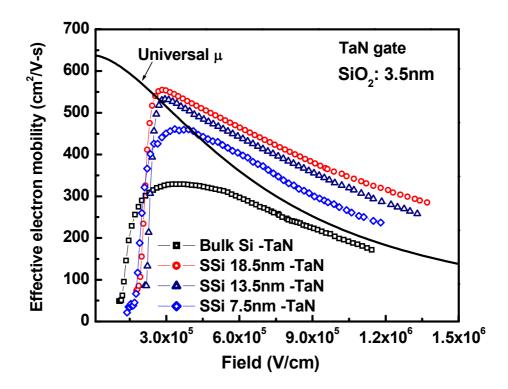

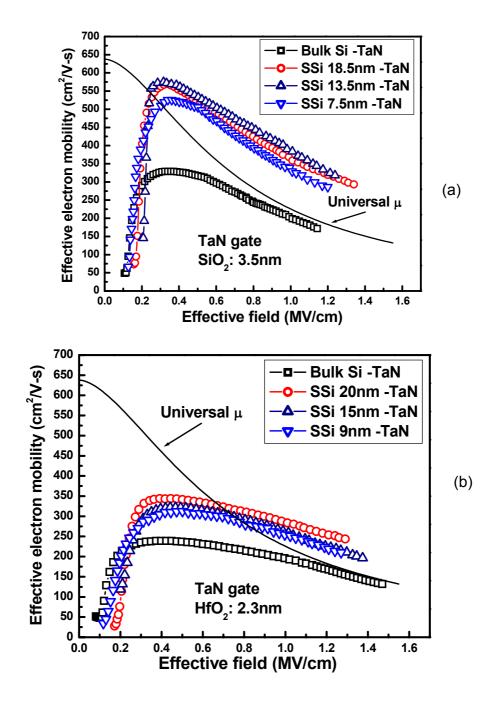

| Figure 6-6  | Effective mobility of SiO <sub>2</sub> nFETs plotted vs. effective field. Three different strained Si               |

|-------------|---------------------------------------------------------------------------------------------------------------------|

|             | thicknesses were employed. Bulk Si nFET was used as a control147                                                    |

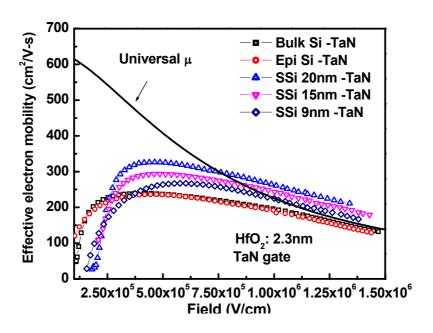

| Figure 6-7  | Effective mobility of HfO <sub>2</sub> nFETs plotted vs. effective field. Three different strained Si               |

|             | thicknesses were employed148                                                                                        |

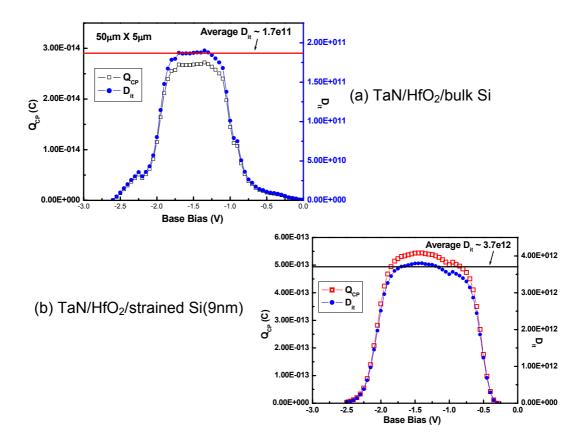

| Figure 6-8  | Charge pumping currents plotted vs. base sweep biases for TaN/HfO <sub>2</sub> devices on (a)                       |

|             | bulk Si; (b) 9nm strained Si. The measurements were carried out at 100kHz150                                        |

| Figure 6-9  | Charge pumping currents plotted vs. amplitude sweep biases for TaN/HfO2 devices                                     |

|             | on (a) bulk Si; (b) 20nm strained Si. The measurements were carried out at 100kHz                                   |

|             | 151                                                                                                                 |

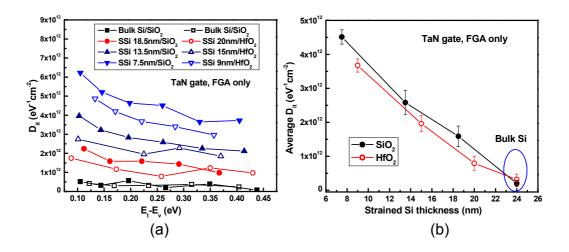

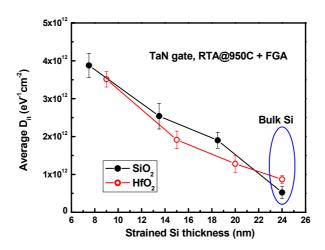

| Figure 6-10 | D <sub>it</sub> measured from two level charge pumping at 100kHz for nFETs on SiO <sub>2</sub> and HfO <sub>2</sub> |

|             | with different strained Si thickness                                                                                |

| Figure 6-11 | D <sub>it</sub> extracted from three level charge pumping as a function of (a)bandgap; (b)                          |

|             | strained Si thickness for strained Si MOSFETs with TaN gates on SiO <sub>2</sub> and HfO <sub>2</sub>               |

|             | 153                                                                                                                 |

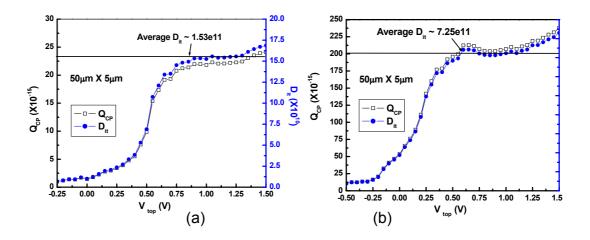

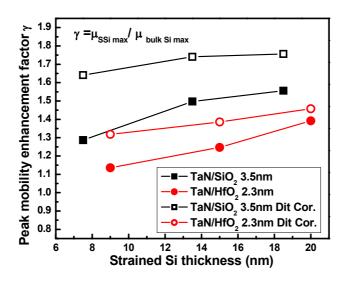

| Figure 6-12 | Effective electron mobility after D <sub>it</sub> corrections for TaN strained Si MOSFETs on SiO <sub>2</sub>       |

|             | and HfO <sub>2</sub> 157                                                                                            |

| Figure 6-13 | Effective electron mobility extracted with D <sub>it</sub> corrections for nMOSFETs on (a) SiO <sub>2</sub>         |

|             | and (b) HfO <sub>2</sub> 158                                                                                        |

| Figure 6-14 | Peak mobility enhancement factor $\gamma$ plotted vs. strained Si thickness                                         |

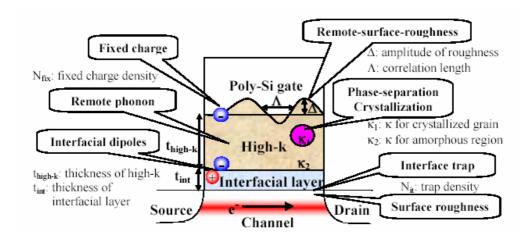

| Figure 6-15 | Possible sources of scattering in high- κ gate stacks                                                               |

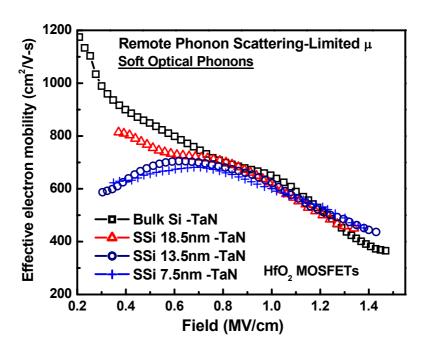

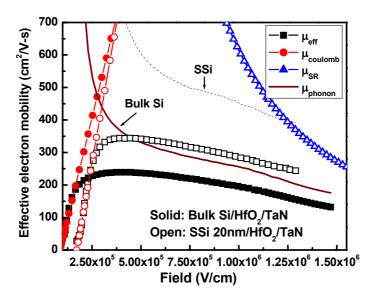

| Figure 6-16 | HfO <sub>2</sub> limited mobility component for bulk Si and strained Si devices plotted as a                        |

|             | function of effective field161                                                                                      |

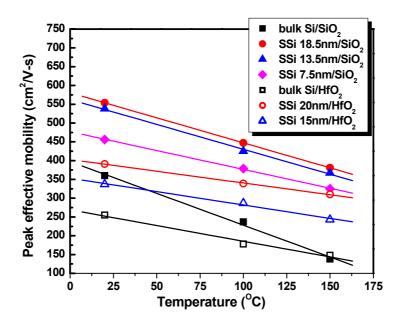

| Figure 6-17 | Peak mobility plotted as a function of temperature for TaN gate MOSFETs on SiO <sub>2</sub>                         |

|             | and HfO <sub>2</sub> dielectrics with bulk Si and/or strained Si channels162                                        |

| Figure 6-18 | D <sub>it</sub> -corrected effective mobility and calculated phonon limited mobility using                          |

|             | Matthiessen's rule for bulk Si and 20nm strained Si nMOSFETs on HfO <sub>2</sub> 165                                |

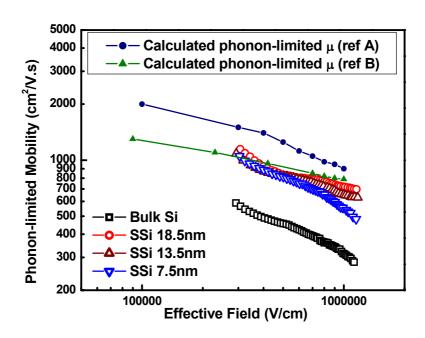

| Figure 6-19 | "Phonon-limited" effective mobility components of n-channel devices plotted as a         |

|-------------|------------------------------------------------------------------------------------------|

|             | function of effective field on bulk Si and strained Si. Theoretical values calculated in |

|             | Ref. A and ref. B are also included                                                      |

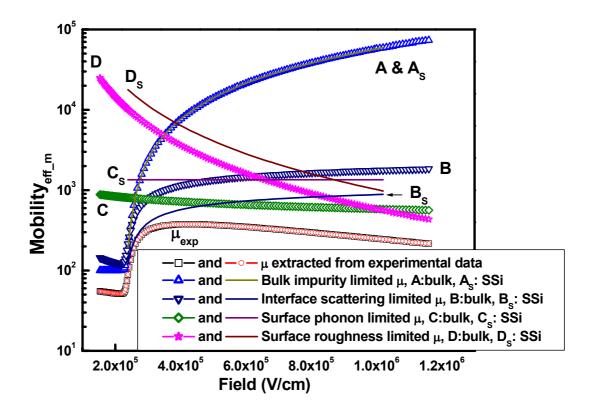

| Figure 6-20 | The phonon, surface roughness and interface scattering mobility components of a          |

|             | strained Si sample simulated by using Hauser's MOB2D model compared to those of          |

|             | a bulk Si sample                                                                         |

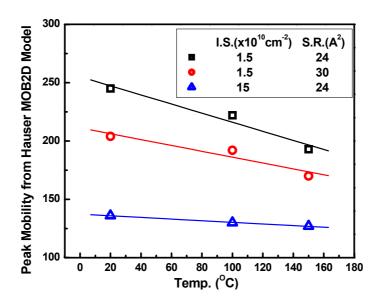

| Figure 6-21 | Modeled peak mobility plotted vs. temperature with different interface scattering        |

|             | density (I.S.) and surface roughness (S.R.) parameter values extracted from the          |

|             | Hauser NCSU MOB2D model and Lazar's Thesis169                                            |

## **List of Tables**

| Near Term2                                       | High performance logic technology requirem                 | Table 1-1 |

|--------------------------------------------------|------------------------------------------------------------|-----------|

| e3                                               | Potential solutions to improve device perform              | Table 1-2 |

| in different directions for a <110>              | Effects of stress on the MOSFET performa                   | Table 1-3 |

| 14                                               | oriented channel                                           |           |

| position used in this work37                     | Typical process conditions for Si and Si <sub>1-x</sub> Ge | Table 2-1 |

| tes42                                            | Metal gate electrode sputtering conditions ar              | Table 2-2 |

| ow43                                             | Summary of strained Silicon MOSFET proce                   | Table 2-3 |

| deposited films as a function of film            | Summary of XRD extracted Ge concentration                  | Table 4-1 |

| °C and the deposition pressure was               | thickness. The deposition temperature was                  |           |

| lve81                                            | 700 mTorr maintained by adjusting the throttl              |           |

| to optimize deposition parameters                | Experimental conditions considered in this                 | Table 4-2 |

| 83                                               | without using the throttle valve                           |           |

| riments87                                        | Process parameters used in HfO <sub>2</sub> formation 6    | Table 4-3 |

| nd leakage current densities before              | Electrical properties extracted from C-V da                | Table 4-4 |

| 88                                               | and after RTA of HfO <sub>2</sub> samples                  |           |

| ETs with polysilicon and TaN gate                | Extracted device parameters for SiO <sub>2</sub> MC        | Table 6-1 |

| ting thickness before gate oxidation.            | electrodes. Strained Si (SSi) thickness is the             |           |

| 140                                              |                                                            |           |

| ETs on SiO <sub>2</sub> and HfO <sub>2</sub> 146 | Extracted device parameters of TaN gate MC                 | Table 6-2 |

| s from two level charge pumping                  | Constants used to extract average Dit vo                   | Table 6-3 |

| 149                                              | measurement                                                |           |

| g to determine the $D_{it}$ of TaN gate          | Parameters used in three level charge pur                  | Table 6-4 |

| 152                                              | devices on SiO <sub>2</sub> and HfO <sub>2</sub>           |           |

## **Chapter 1 Introduction**

#### 1.1 CMOS Technology Scaling

Integrated circuit (IC) technology has been improving for over 40 years, following Moore's Law by consistently scaling the design rules, increasing the chip and wafer size, and cleverly improving the designs of devices and circuits [1, 2]. For both memory and logic chips, the speed and density increased exponentially while the power dissipation and cost per function decreased. For example, the speed of microprocessors has been doubling approximately every three years, increasing from 2 MHz for the Intel® 8080 in the mid-1970s to over 1 GHz for the current chips [3]. Continuous MOSFET scaling resulted in advancing from the  $\sim$  8  $\mu$ m technology in 1972 to the current 90 nm technology, which corresponds to a reduction of  $\sim$  0.87 per year [4]. If the scaling continues at this rate, the IC industry will face increasing difficulties due to the fundamental limits of certain devices and materials.

The Semiconductor Industry Association (SIA) has been publishing roadmaps since 1992. The most recent 2004 *International Technology Roadmap for Semiconductors* (ITRS) predicts the next 14 years [2]. In comparison to the 1999 ITRS [5], one major change is acceleration in the scaling of the physical gate length (L<sub>g</sub>) driven by the industry's need to maximize the chip speed [4]. Table 1-1 presents all the parameters required by High performance logic technology in the next several years as projected by the 2004 ITRS.

Table 1-1 High performance logic technology requirements -- Near Term

| Year of Production                                                                                           | 2003           | 2004     | 2005     | 2006     | 2007     | 2008     | 2009     |

|--------------------------------------------------------------------------------------------------------------|----------------|----------|----------|----------|----------|----------|----------|

| Technology Node                                                                                              |                | hp90     |          |          | hp65     |          |          |

| DRAM ½ Pitch (nm)                                                                                            | 100            | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU/ASIC Metal 1 (M1) ½ Pitch (nm)                                                                           | 120            | 107      | 95       | 85       | 76       | 67       | 60       |

| MPU/ASIC ½ Pitch (nm)                                                                                        | 107            | 90       | 80       | 70       | 65       | 57       | 50       |

| MPU Printed Gate Length (nm)                                                                                 | 65             | 53       | 45       | 40       | 35       | 32       | 28       |

| MPU Physical Gate Length (nm)                                                                                | 45             | 37       | 32       | 28       | 25       | 22       | 20       |

| Physical gate length high-performance (HP) (nm) [1]                                                          | 45             | 37       | 32       | 28       | 25       | 22       | 20       |

| EOT: equivalent oxide thickness (physical) for high-performance (nm) [2]                                     | 1.3            | 1.2      | 1.1      | 1.0      | 0.9      | 0.8      | 0.8      |

| Electrical thickness adjustment for gate depletion and inversion layer effects (nm) [3]                      | 0.8            | 0.8      | 0.7      | 0.7      | 0.4      | 0.4      | 0.4      |

| Equivalent electrical oxide thickness in inversion (nm) [4]                                                  | 2.1            | 2.0      | 1.8      | 1.7      | 1.3      | 1.2      | 1.2      |

| Nominal gate leakage current density limit (at 25°C) (A/cm²) [5]                                             | 2.2E+02        | 4.5E+02  | 5.2E+02  | 6.0E+02  | 9.3E+02  | 1.1E+03  | 1.2E+03  |

| Nominal power supply voltage (V <sub>dd</sub> ) (V) [6]                                                      | 1.2            | 1.2      | 1.1      | 1.1      | 1.1      | 1.0      | 1.0      |

| Saturation threshold voltage (V) [7]                                                                         | 0.21           | 0.20     | 0.20     | 0.21     | 0.18     | 0.17     | 0.16     |

| Nominal high-performance NMOS sub-threshold leakage current, $I_{sd,leak}$ (at 25°C) ( $\mu A/\mu m$ ) [8]   | 0.03           | 0.05     | 0.05     | 0.05     | 0.07     | 0.07     | 0.07     |

| Nominal high-performance NMOS saturation drive current, $I_{d,sat}$ (at $V_{dd}$ , at 25°C) (mA/mm) [9]      | <b>♦</b> 980   | 1110     | 1090     | 1170     | 1510     | 1530     | 1590     |

| Required "mobility/transconductance improvement" factor [10]                                                 | 1.0            | 1.3      | 1.3      | 1.4      | 2.0      | 2.0      | 2.0      |

| Sub-threshold slope adjustment factor (full depletion/multiple-gate effects) $(0-1)$ [11]                    | 1.0            | 1.0      | 1.0      | 1.0      | 1.0      | 0.8      | 0.7      |

| Effective saturation carrier velocity enhancement factor (due to quasi-ballistic transport) [12]             | 1.0            | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      | 1.0      |

| Parasitic source/drain series resistance (R <sub>sd</sub> ) (Ohm-µm) [13]                                    | <b>♦ 180</b>   | 180      | 180      | 171      | 162      | 153      | 144      |

| Ideal NMOS device gate capacitance (F/µm) [14]                                                               | 7.40E-16       | 6.39E-16 | 6.14E-16 | 5.69E-16 | 6.64E-16 | 6.33E-16 | 5.76E-16 |

| Parasitic fringe/overlap capacitance (F/µm) [15]                                                             | 2.40E-16       | 2.40E-16 | 2.40E-16 | 2.30E-16 | 2.20E-16 | 2.00E-16 | 1.90E-16 |

| High-performance NMOS intrinsic delay, $\tau = C_{\text{gate}} * V_{\text{dd}} / I_{\text{d,sat}}$ (ps) [16] | <b>1.20</b>    | 0.95     | 0.86     | 0.75     | 0.64     | 0.54     | 0.48     |

| Relative NMOS intrinsic switching speed, 1/τ, normalized to 2003 [17]                                        | <b>◆</b> 1.00  | 1.26     | 1.39     | 1.60     | 1.86     | 2.20     | 2.49     |

| Nominal logic gate delay (NAND Gate) (ps) [18]                                                               | <b>◆</b> 30.24 | 23.94    | 21.72    | 18.92    | 16.23    | 13.72    | 12.13    |

| NMOSFET power-delay product (J/µm) [19]                                                                      | 1.41E-15       | 1.27E-15 | 1.03E-15 | 9.66E-16 | 1.07E-15 | 8.33E-16 | 7.66E-16 |

| NMOSFET static power dissipation due to drain and gate leakage (W/µm) [20]                                   | 3.96E-07       | 6.60E-07 | 6.05E-07 | 6.05E-07 | 8.47E-07 | 7.70E-07 | 7.70E-07 |

Manufacturable solutions exist, and are being optimized

Manufacturable solutions are known

Interim solutions are known

Manufacturable solutions are NOT known

For digital circuits, the gate delay is defined as  $\tau = CV/I$  where C is the gate capacitance, V is the voltage swing and I is the drive current. While the drive current is increasing linearly with scaling the transistor off current is increasing exponentially. Both a large drive current and a small standby power are needed. Device performance can improve by 1) inducing a larger charge density for a given gate voltage drive; 2) enhancing the carrier transport; 3) ensuring device scalability to

achieve a shorter channel length; and 4) reducing parasitic capacitances and parasitic resistances [6]. Table 1-2 summarizes these opportunities/challenges and corresponding proposed technology options. These options can be classified into two categories: new materials and new device structures, which are usually related.

Table 1-2 Potential solutions to improve device performance [6].

| Source of improvement                                   | Parameters affected                                                                                    | Method                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |

|---------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Charge<br>density                                       | <ul> <li>S (inverse subthreshold slope)</li> <li>Q<sub>inv</sub> at a fixed I<sub>off</sub></li> </ul> | <ol> <li>Double-gate FET.</li> <li>Lowered operating temperature.</li> </ol>                                                                                                                                                                                                                                                                                                                                                                  |  |  |

| Carrier<br>transport                                    | <ul> <li>Mobility (μ<sub>eff</sub>)</li> <li>Carrier velocity</li> <li>Ballistic transport</li> </ul>  | <ol> <li>Strained silicon.</li> <li>High-mobility and saturation-velocity materials (e.g., Ge, InGaAs, InP).</li> <li>Reduce mobility degradation factors (e.g., reduced transverse electric field, reduced Coulomb scattering due to dopants, reduced phonon scattering).</li> <li>Shorter channel length.</li> <li>Lowered operating temperature.</li> </ol>                                                                                |  |  |

| Parasitic resistance                                    | • R <sub>ext</sub>                                                                                     | Extended/raised source/drain.     Low-barrier Schottky contact.                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| Parasitic capacitance                                   | • C <sub>jn</sub> • C <sub>GD</sub> , C <sub>GS</sub> , C <sub>GB</sub>                                | SOI.     Double-gate FET.                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |

| Ensuring device scalability to a shorter channel length | <ul> <li>Generalized scale length (λ)</li> <li>Channel length (L<sub>g</sub>)</li> </ul>               | <ol> <li>Maintaining good electrostatic control of channel potential (e.g., double-gate FET, ground-plane FET, and ultrathin-body SOI) by controlling the device physical geometry and providing means to terminate drain electric fields.</li> <li>Sharp doping profiles, halo/pocket implants.</li> <li>High gate capacitance (thin gate dielectrics, metal gate electrode) to provide strong gate control of channel potential.</li> </ol> |  |  |

As summarized in the table above, strained silicon could be one of the candidates to enhance the carrier transport. A high dielectric constant ( $\kappa$ ) material is required to achieve low equivalent oxide thickness (EOT). In addition, metal gate electrodes are employed to integrate with high- $\kappa$  dielectrics as well as silicon dioxide

to ensure the device scalability and eliminate problems brought about by polysilicon gates. All the advantages and current issues of strained silicon, high-κ dielectrics, and metal gates will be discussed in detail in the following sections.

#### 1.2 Strained Silicon Technology

## 1.2.1 Why Is Strained Silicon Required for Future CMOS Devices

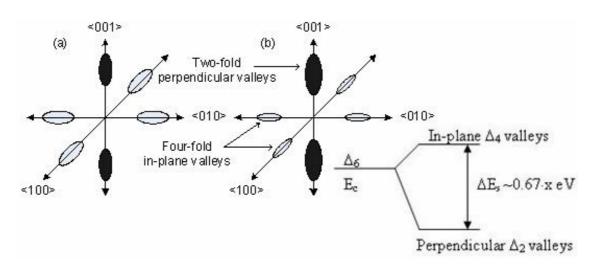

Alternative channel materials that offer higher carrier mobilities are needed to improve the carrier transport properties of future MOSFETs. Unfortunately, replacing Si with a new material does not necessarily provide the performance enhancement expected from the higher mobility due to other shortcomings or performance challenges of the new material [7]. This is one of the key reasons behind the recent excitement over strained Si. Essentially, it is now well established that without changing the channel material, significant enhancements in device performance are possible using strained silicon [8-23]. The theory of mobility enhancement in strained Si is still evolving [10]. The most commonly accepted explanation is that under the biaxial tensile strain, the six-fold degenerate valleys in Si are split into two groups. The group with the lower energy is two fold degenerate (labeled as  $\Delta_2$  in Figure 1-1), which is the primary contributor to carrier transport at low fields. The in-plane effective mass of the electrons occupying these bands is approximately equal to the Si transverse effective mass  $(m_t^*=0.19m_0)$ . On the other hand, the effective mass perpendicular to the transport plane is equal to the longitudinal effective mass  $(m_l^*=0.92m_0)$ . The schematic representation of the energy ellipses is shown in Figure 1-1[8]. The energy of the conduction-band minima of the four valleys on the in-plane <100> axes rises with respect to the energy of the two valleys on the <100> axes

perpendicular to the plane [24, 25], as shown in Figure 1-2 (a) [26]. The energy between the two-fold degenerate and the four-fold degenerate valleys,  $\Delta E_{\rm strain}$ , is given by  $\Delta E_{\rm strain} = 0.67 x \, eV$ , where x is the Ge content of the relaxed  ${\rm Si}_{1-x}{\rm Ge}_x$  substrate [9]. It should be noted that even in an unstrained Si MOS inversion layer there is band splitting between the sub-band energies in the two and the four-fold valleys due to quantization in the inversion layer. In a strained Si MOS inversion layer, the band splitting of the conduction band  $\Delta E_{\rm strain}$  is superimposed on this quantization, as schematically shown in Figure 1-2 (b) [26]. The electrons populate the lower  $\Delta_2$  valleys with lighter effective mass, which results in the reduction of the average conductivity effective mass.

Figure 1-1 Schematic representation of the strain induced conduction band splitting in silicon [8].

Figure 1-2 Energy alignment of the Si conduction band with and without the tensile strain in (a) bulk and (b) inversion layer, respectively.

The other mechanism of mobility enhancement proposed by Takagi et al. [26] is the suppression of intervalley phonon scattering due to the energy splitting between the two fold and the four fold valleys. Intervalley phonon scattering is an inelastic process associated with the absorption or the emission of the relevant phonons with a large wave vectors. Thus, if the amount of the band splitting between the two and the four fold valleys becomes larger than the energy of the relevant phonons, the scattering probability will be significantly reduced. Therefore, better enhancement of the electron low field mobility will be achieved with higher Ge content in the relaxed Si<sub>1-x</sub>Ge<sub>x</sub> substrate.

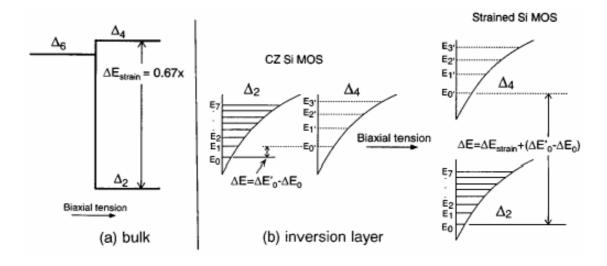

In unstrained material, the valence band maximum is composed of three bands: the degenerate heavy-hole (HH) and light-hole (LH) bands at k=0, and the split-off (SO) band which is slightly lower in energy, as shown in Figure 1-3 [12]. The biaxial stress can be resolved into a hydrostatic and a uniaxial stress component.

The hydrostatic stress equally shifts all three valence bands, while the uniaxial stress lifts the degeneracy between LH and HH bands by lifting the LH band higher than HH. The SO band is also lowered with respect to the other two bands. This leads to the population of holes in the energetically favorable LH like band. Application of stress also changes the shape of the bands as shown in Figure 1-3 (b). Therefore, due to the band deformation, the in-plane transport mass becomes smaller and the interband scattering is also suppressed. Thus the hole mobility is improved.

Figure 1-3 Simplified hole valence band structure for longitudinal in plane direction (a) unstrained and (b) strained silicon [27].

The main difference between the effects on electron and hole mobilities is that the mobility of holes can be enhanced only at lower electric fields while the enhancement can be achieved at higher vertical electric fields for electrons. Fischetti et al. showed that the loss in hole mobility enhancement at higher fields was due to reduction in the separation between the light hole and heavy hole bands ( $\Delta_{LH-HH}$ ) [28]. Based on the experimental data, it was speculated that this was due to the confining surface potential operating against the applied biaxial stress and trying to reduce the separation between the LH and HH bands [28]. The utilization of uniaxial strained

silicon devices can improve hole mobility at both low and high electric fields, which will be presented in section 1.2.3.

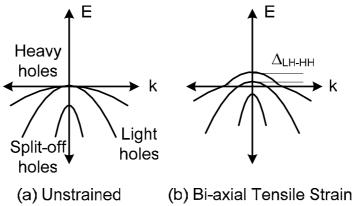

#### 1.2.2 Biaxial Strained Silicon and Device Applications

Strain in Si can be introduced in various ways. The most commonly used method is to deposit a thin Si epitaxial layer on top of a thick relaxed SiGe buffer layer [11, 14, 29]. Silicon and germanium, both crystallizing in the diamond lattice, can form a continuous series of Si<sub>1-x</sub>Ge<sub>x</sub> solid solutions with x ranging from 0 to 1. The lattice constants are 0.5431 nm for Si and 0.5657 nm for Ge. The lattice mismatch between Si and Ge, herein referred to as f, is about 4.2 %, which is sufficiently small. Therefore the deposited first several atomic layers will be strained to match the substrate and a coherent interface will be formed. The structure stores a high amount of elastic strain energy because interatomic bond lengths in the epilayer are stretched or compressed compared to their equilibrium values. At some epilayer thickness, generally called the critical thickness  $h_c$ , it becomes energetically favorable to relieve the elastic strain energy by introducing misfit dislocations and allowing the epilayer to relax towards its bulk lattice parameter. The critical thickness has been first calculated by several groups based on different models [30-35]. When the thickness of Si<sub>1-x</sub>Ge<sub>x</sub> alloy exceeds the critical thickness, the alloy will be called a "relaxed" Si<sub>1-x</sub>Ge<sub>x</sub> film. The lattice parameter could be calculated according to the Vegard's law, assuming the film is fully relaxed:

$$a_{SiGe}(x) = a_{Si} \cdot (1 - x) + a_{Ge} \cdot x \tag{1.1}$$

The primary function of this relaxed SiGe layer is to serve as a "virtual substrate" creating tensile strain in the top Si epilayer, as shown in Figure 1-4.

However it has no impact on the improvement of device performance. The thickness of strained Si must be relatively thin so that the strain will not be relaxed through misfit dislocations. Figure 1-4 (c) shows the band offset for a strained-Si film grown on relaxed (001) SiGe substrate. In this case, a large band offset is obtained in both the conduction and valence bands relative to the relaxed Si<sub>1-x</sub>Ge<sub>x</sub> layer and is called a type II band offset [25, 36]. This allows both electron and hole confinements in the strained Si layer, making it useful for both n- and p-type devices for strained-Si/SiGe based CMOS technology. The critical thickness of Si layers grown on relaxed uniform SiGe layers has also been calculated [37].

Figure 1-4 Schematic illustrations of (a) equilibrium lattices and (b) pseudomorphic strained Si on relaxed SiGe [8] (c) band alignments between strained Si and the relaxed SiGe virtual substrate [38].

Recent work has provided encouraging experimental data showing the mobility enhancement with different devices structures, including both n-channel and p-channel devices. Research on strained Si MOSFETs can be grouped into two categories: "bulk" strained Si on relaxed SiGe FETs (SS FETs) and strained Si on relaxed SiGe on insulator FETs (SGOI FETs). Recent work indicates that a conventional CMOS process flow can be adopted while still achieving the mobility and current drive enhancement [20]. Fabrication processes such as source/drain extensions and halos, channel ion implantation, and associated high temperature activation anneals are shown to have no adverse impact on device characteristics.

The first strained Si n-MOSFETs were fabricated on relaxed Si<sub>0.7</sub>Ge<sub>0.3</sub> substrates and provided about 70% electron mobility enhancement with a vertical effective electric field ( $E_{eff}$ ) up to 0.6 MV/cm [21]. At a lower V<sub>GS</sub>, the current drive enhancement over the unstrained silicon control is as large as 50%, while at V<sub>GS</sub> = 0.8 V, the current drive of a strained Si device is ~ 35 % higher [6]. Figure 1-5 shows both the experimental data and the theoretical values of the phonon limited electron mobility enhancement versus the substrate Ge content [22]. With the Ge content above 20 %, the mobility enhancement factor, r, saturates near 1.8, in agreement with calculations of the impact of strain on the mobility. Experiments also indicate that for electrons, the strain induced mobility enhancement factor is relatively constant with  $E_{eff}$ . For the same channel length, the current drive enhancements can be significantly changed due to the variation of doping profiles, strain induced band changes, and oxide thickness even for nanoscale MOSFETs.

Figure 1-5 Measured (symbols) effective mobility enhancement ratios, *r*, compared to calculations for the phonon limited MOS mobility (solid line) for strained Si *n*-MOSFETs [22].

The combination of high mobility strained Si devices with SOI structures will provide additional advantages such as reduced parasitic capacitances, improved isolation, and reduced short channel effects. Strained Si-on-insulator (SSOI) MOSFETs can be fabricated from strained silicon grown on relaxed Si<sub>1-x</sub>Ge<sub>x</sub>-on-insulator (SGOI) virtual substrates [12, 15-19, 23, 37, 38]. SGOI can be achieved via several approaches such as "etch-back" and "smart-cut" processes [12, 15-17, 23], SIMOX technology [14, 18, 37], and Ge condensation techniques [12, 19, 38].

The Si valence band degeneracy is also split by biaxial tensile strain induced by growth in relaxed  $Si_{1-x}Ge_x$  (~ 40 meV/10 % Ge). Therefore, hole mobility enhancement can also be obtained with strained Si p-MOSFETs. Generally, larger strain is required to get valence band splitting, which means higher Ge content is needed in the relaxed SiGe virtual substrate. Recent research data is shown in

Figure 1-6 [22] where the hole mobility enhancement is primarily achieved in the low  $E_{\rm eff}$  range (<1 MV/cm) and the mobility enhancement ratio approaches 1 with the Ge content below 30 % in the underlying relaxed SiGe substrate. Unlike electron mobility, hole mobility enhancement is reduced for higher  $E_{\rm eff}$ . To improve the hole mobility further, the substrate Ge content should be increased. This could be the solution for the single strained Si channel structures, which is feasible by using SIMOX and Ge condensation techniques.

Figure 1-6 Comparison of hole mobility enhancement ratios in strained Si p-MOSFETs as a function of vertical effective field,  $E_{\rm eff}$ . The numbers beside the data are the substrate Ge percent.

#### 1.2.3 Uniaxial Strained Silicon and Device Applications

There are various methods to induce uniaxial stress, which differ from one company to another. The thermal mismatch of silicon, the isolation materials, novel

junction structures, and gate electrodes have been reported recently to cause sufficient local strain, which can alter device characteristics [28, 39-47].

Intel demonstrated strained silicon MOSFETs with uniaxial strain based on the structure shown in Figure 1-7[39, 40]. Piezoresistance coefficients in silicon were used to model the behavior of uniaxial stress in MOSFETs. This model is only valid for small stress values where the mobility enhancement mainly results from the change in the conductivity effective mass. This is a good assumption since Intel used low stress levels for its MOSFETs and fewer defects are created requiring less alteration to the existing technology. Detailed discussions of the effect of mechanical stress on the mobility can be found in literature [39-41]. A summary of the effects of various stress components on the channel mobility is listed in Table 1-3. It can be seen that in order to achieve mobility enhancement for a <110> channel, longitudinal compressive stress for pMOSFETs and longitudinal tensile and out of plane compressive stress for nMOSFETs are most effective. Therefore SiGe source/drain junctions on the PMOS and a tensile capping layer on the NMOS were employed by Intel to induce strain.

Figure 1-7 Schematic showing different types of strain induced in the silicon channel [40].

Table 1-3 Effects of stress on the MOSFET performance in different directions for a <110> oriented channel [39, 41, 42].

| Directions         | NMOS                | PMOS    |

|--------------------|---------------------|---------|

| Along channel (x)  | Tension Compression |         |

|                    | +++                 | ++++    |

| Across channel (z) | Tension             | Tension |

| , ,                | + +                 | +++     |

| Vertical (y)       | Compression         | Tension |

|                    | ++++                | +       |

In addition to achieving a higher hole mobility enhancement at low vertical electric fields deduced from the piezoresistance coefficients [43], uniaxial strain also maintains this enhancement at higher electric fields, which has been demonstrated experimentally. Fischetti et al. has theoretically explained the loss of hole mobility enhancement at higher fields by using reduced separation between the LH and HH like bands [28]. However, for uniaxial stress, the confining surface potential does not reduce the strain induced band separation as it does in the biaxial case. This can be attributed to the band warping caused by the uniaxial stress to create an advantageous out of plane effective mass for the top energy band. Therefore, the hole population in the energetically favorable LH like band would be enhanced and hence the mobility enhancement at higher fields would be maintained.

For the corresponding NMOS device fabricated by Intel, a nitride capping layer which created longitudinal tensile and out of plane compressive stress in the silicon channel was used to obtain the electron mobility enhancement [39]. The enhancement in performance was shown to be strongly dependent on the thickness of the capping layer. As shown in Figure 1-8, a capping layer thickness of ~75 nm showed 10 % improvement in drive current.

Figure 1-8 Electron saturated drive current improvement verses nitride thickness [40].

Texas Instruments (TI) also presented PMOS transistors with a channel length of 37 nm built on successful integration of a recessed SiGe epitaxial layer at the drain extension location. Compressive stress induced by the SiGe layer resulted in 35 % improvement in current drive [44]. Yang et al. reported a high performance CMOS flow in which nitride contact liners were used as dual stress liners (DSL) to induce both tensile and compressive stress achieving mobility enhancement for both electrons and holes. This DSL approach results in 15 % and 32 % effective drive current enhancement for nFET and pFET, respectively and a saturated drive current enhancement of 11 % for nFET and 20 % for pFET [45]. Strain Enhancing Laminated Si<sub>3</sub>N<sub>4</sub> (SELS) was employed by Fujitsu [46] using a new process flow in which SELS was formed selectively only on the nMOS gate. Multiple layers of Si<sub>3</sub>N<sub>4</sub> created higher strain at the corner sidewalls enhancing the channel strain. Drive

currents of  $1120\mu\text{A}/\mu\text{m}$  and  $690\mu\text{A}/\mu\text{m}$  at  $V_{dd}$ = $1V/I_{off}$ = $100\text{nA}/\mu\text{m}$  were demonstrated for a 37 nm gate nMOS and a 45 nm gate pMOS, respectively. Uniaxial strain was also induced by selective epitaxy of silicon carbide (SiC) in the source and drain (S/D) regions of sub 100nm gate nMOS transistors [47]. The carbon mole fraction was 1.3 % such that the lattice mismatch between SiC and Si was 0.65%, resulting in tensile strain along the Si channel and compressive strain normal to the channel. Both the tensile and compressive stress contributed to substantial electron mobility enhancement and ~50 % enhancement in drive current was obtained for a gate length of 50 nm.

#### 1.3 Alternative High Dielectric Constant Gate Insulator Materials

#### 1.3.1 Why Are High K Dielectrics Required

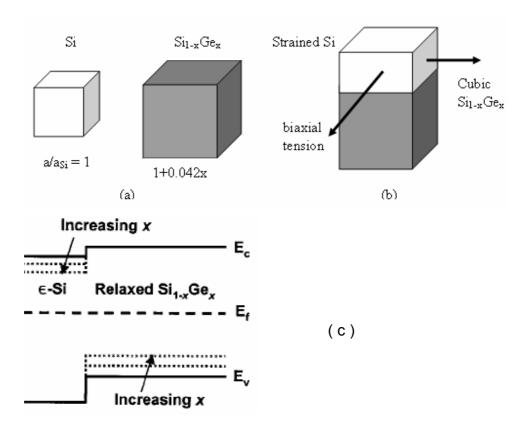

One of the biggest concerns in modern CMOS technology is the gate dielectric. Silicon dioxide ( $SiO_2$ ) has been the ideal gate dielectric because of its amorphous structure, a large band gap of ~ 9 eV, insolubility in water, ability to serve as a separator between metal conducting layers and silicon substrates, and its compatibility with Si having low interface state densities [48]. As the gate oxide begins to scale down to the ultra thin oxide regime, the direct tunneling current increases [49]. In addition, quantum mechanical effects and the polysilicon depletion effect can be amplified as the  $SiO_2$  thickness is reduced, which results in an increase in the effective dielectric thickness [50, 51]. Due to these limitations of  $SiO_2$ , alternative gate dielectrics with higher dielectric constant are required such that physically thicker dielectrics can be used to reduce the probability of electrons and holes tunneling.

Besides the high permittivity, additional requirements for alternate high-k dielectrics include a large band gap for appropriate barrier height, thermodynamic stability on Si, noncrystalline film morphology, ability to form a high quality interface with Si (with low fixed charge and low interface charge), and compatibility with gate electrodes and existing CMOS processing. Current research is focused on dielectrics with moderate k since the permittivity must be balanced with the band offset, which is the barrier height for tunneling processes. Figure 1-9 shows the key properties (dielectric constants and band offsets) of potential high-κ dielectric candidates [52, 53]. Therefore, to achieve low gate leakage, those materials with band offsets less than 1 eV will not be desirable candidates as gate insulators. Most of the high-k metal oxide systems investigated so far have unstable interfaces with Si. Therefore an interfacial layer is formed which plays a dominant role in the device electrical properties. It is necessary to study the thermodynamics of these systems thereby attempting to control the interface between high-k and Si [54]. Currently, most of the high-κ materials show D<sub>it</sub> of 10<sup>11</sup>-10<sup>12</sup> cm<sup>-2</sup>-eV<sup>-1</sup> and fixed charge density >10<sup>12</sup> cm<sup>-2</sup> at the interface, which is higher than the typical midgap interface density of Si (2 x 10<sup>10</sup> cm<sup>-2</sup>) [55-58]. It is desirable to select a material which remains amorphous throughout the entire CMOS process since amorphous films exhibit isotropic electrical properties and will not suffer from grain boundaries. The last concern is the compatibility, i.e. the deposition process for high-k dielectrics must be compatible with conventional CMOS processing based on the consideration of cost and throughput.

Figure 1-9 Band offset calculations for a number of potential high-κ gate dielectric materials [52, 53].

#### 1.3.2 Hafnium Based Dielectrics

For the past several years,  $HfO_2$  and its silicates have received significant attention as alternative gate dielectrics due to their thermodynamic stability on Si and their large barrier heights [56, 59-61]. Lee et al. achieved an ultra thin  $HfO_2$  gate dielectric with 0.9 nm EOT and a Pt gate using an optimized reactive dc magnetron sputtering process [56]. It is found that the dielectric constant of  $HfO_2$  was ~28 and that the EOT was stable up to 700 °C. Lee et al. also reported a 1.04 nm EOT  $HfO_2$  with polysilicon gate without any barrier layer [59]. They reported that their  $HfO_2$  film remained high quality after high temperature dopant activation (950 °C for 30 seconds) and had very low leakage current (0.23 mA/cm² at Vg = 1 V). Wilk et al. reported an EOT less than 1.8 nm for a 5 nm  $Hf_6Si_{29}O_{65}$  film, which yields a dielectric constant ~11 [60]. It is not conclusive, however, that  $HfO_2$  or Hf silicates will be the

best candidate as the gate insulator for 65 nm gate length CMOS. Researchers are still continuously searching for a material which can fulfill all the gate dielectric requirements.

#### 1.3.3 Additional Problems with High κ Dielectrics

Challenges arise from the processing and integration of high- $\kappa$  dielectrics, especially during those steps preformed at high temperature. The intrinsic limitation of high- $\kappa$  dielectrics is that a SiO<sub>2</sub> rich interfacial layer will be formed during the deposition of high- $\kappa$  on Si, which makes it very difficult to scale the EOT. Recently, reports of nitrogen based materials and nitrogen annealing have shown the decrease or elimination of the interfacial layer [62-65]. Thermal stability is another key requirement for high- $\kappa$  dielectrics since junction activation is always performed at a high temperature in conventional CMOS processing. The possible formation of silicates between the dielectric and Si substrate as well as other probable reactions between high- $\kappa$  dielectric with metal gates will inevitably increase the EOT and have other adverse impacts on the channel. High temperature processes can also change the film morphology of high- $\kappa$  dielectrics, resulting in crystalline or polycrystalline materials and thus increased leakage.

A lot of attention has been placed on the mechanisms of mobility degradation in high-κ devices. NMOS device mobility degradation is a more significant problem than that of PMOS degradation. Fischetti et al. reported that the high permittivity of materials like HfO<sub>2</sub> and ZrO<sub>2</sub> result in the presence of a large part of soft optical phonons providing a long-range scattering of electrons in the Si inversion layer [66]. Thus the electron mobility could be reduced by as much as a factor of 3 due to this

unavoidable scattering mechanism. Remote charge scattering may be another component limiting the carrier mobility in high-κ devices [67]. An in depth study to understand these additional scattering mechanisms in high-κ gate stacks is necessary to minimize the mobility degradation.

#### 1.4 Metal Gate Electrodes

#### 1.4.1 Why Do We Need Metal Gates

There are several limitations of the present polysilicon gate for submicron CMOS technology [68]. Modern CMOS processing uses n+ polysilicon gates for NMOS and p+ polysilicon gates for PMOS, which is normally achieved by ion implantation and subsequent annealing. During the doping process, dopant penetration into the thin gate dielectric may occur, especially for boron, and can shift the device threshold voltage. For deep submicron devices, ultra shallow junctions are required. Therefore, both the implantation energy and the dopant activation temperature are reduced, resulting in a low active dopant concentration in the externally doped polysilicon. The doping level of polysilicon can also be reduced due to dopant segregation during silicidation and dopant evaporation during activation annealing [69]. A polysilicon depletion layer is formed at the polysilicon/gate oxide interface and can decrease both the drive current and transconductance of the transistor [69]. The poly-Si depletion becomes more severe as the effective dielectric thickness is reduced. Also, the sheet resistance of the polysilicon gate can be high because of the scaling of polysilicon thickness which then limits the MOSFET circuit speed. Replacing gate electrodes with metal gates will be able to eliminate these issues.

Furthermore, Hobbs et al. have reported that Fermi level pinning problems occur when polysilicon gate electrodes are deposited on high-κ dielectrics [70]. For Hf based dielectrics, the interfacial Si-Hf bonds create dipoles which pin the Fermi level right below the polysilicon conduction band, hence increasing the threshold voltage. Therefore, metal gate electrodes are required for alternative gate dielectrics.

#### 1.4.2 Current Candidates: Advantages and Problems

Candidates for new metal electrodes are required to have good thermal and chemical stability, as well as process compatibility with current CMOS technology and future high-k dielectrics. A desirable metal gate should have an appropriate work function for NMOS or PMOS devices. Therefore, the work function needs to be within 0.2 eV of the conduction and valence band edges of Si [71]. In addition, a low diffusivity to oxygen and other dopants of the metal gate is necessary. Dual metal gates or midgap metal gate electrodes can be used in CMOS processing. There has been research on fabricating CMOS with a single midgap metal gate to simplify the process. However, due to the tradeoff of low channel doping requested by low threshold voltage and control of short channel effects, the mid-gap metal gate is not suitable for submicron devices [72].

Work functions of different metals have been measured by evaluating the flat band voltages on SiO<sub>2</sub>, ZrO<sub>2</sub> and ZrSiO<sub>4</sub> [71]. It was found that the work functions of AI, Ta, Mo, Ti, Hf, and Zr were near the conduction band of Si, hence they could be potential candidates for NMOS. On the other hand, the work functions of Pt, Ru, Rh, Co, Pb, and RuO<sub>2</sub> were near the valance band, so these metals appear to be suitable for PMOS as gate electrodes. There are also conducting metal nitrides such