#### **ABSTRACT**

KANG, INKUK Formation of  $N^+P$  Junctions Using In-situ Phosphorus Doped Selective  $Si_{1-x}Ge_x$  Alloys for CMOS Technology Nodes Beyond 50nm. (Under the direction of Dr. Mehmet C. Öztürk.)

As CMOS integrated circuits are scaled beyond the 50nm regime, conventional source/drain junction and contact technologies can no longer satisfy the requirements of MOSFETs, which require super-abrupt doping profiles and extremely low contact resistivities. To address these challenges, selective Si<sub>1-x</sub>Ge<sub>x</sub> source/drain technology was proposed by this laboratory. In this approach, in-situ doped Si<sub>1-x</sub>Ge<sub>x</sub> layers are selectively deposited in recessed source/drain regions. Since the dopants occupy substitutional sites during epitaxial growth, high temperature annealing is not required for dopant activation, which eliminates diffusion and provides abrupt doping profiles. Furthermore, smaller bandgap of Si<sub>1-x</sub>Ge<sub>x</sub> reduces the metal-semiconductor barrier height, an essential requirement for achieving a substantial reduction in contact resistivity.

This thesis focuses on selective rapid thermal chemical vapor deposition of in-situ phosphorus doped  $Si_{1-x}Ge_x$  alloys intended for this application. Experiments were carried out to study electrical properties of the in-situ doped layers with emphasis on maximizing the active carrier concentration. Active phosphorus levels in the range of  $2-5 \times 10^{20}$  cm<sup>-3</sup> were obtained.

The deposited layers were used to fabricate pn junctions with excellent reverse leakage characteristics. Junctions fabricated on lightly doped substrates exhibited behavior equivalent to best junctions in spite of the lattice mismatch between the Si substrate and the phosphorus doped Si<sub>1-x</sub>Ge<sub>x</sub>. Junctions fabricated on heavily doped substrates suffered from band to band tunneling, which is expected regardless of the junction formation technique.

Deposition selectivity of the process was studied and determined that high flows of PH<sub>3</sub> could degrade the selectivity. An alternative deposition process based on alternating periods of deposition and etching was developed, which provided substantial improvements in deposition selectivity.

# FORMATION OF N<sup>+</sup>P JUNCTIONS USING IN-SITU PHOSPHORUS DOPED SELECTIVE $SI_{1-X}GE_X$ ALLOYS FOR CMOS TECHNOLOGY NODES BEYOND 50 NM

by

#### **INKUK KANG**

A dissertation submitted to the Graduate Faculty of North Carolina State University in partial fulfillment of the requirements for the Degree of Doctor of Philosophy

#### **ELECTRICAL ENGINEERING**

|                | Raleigh                                             |

|----------------|-----------------------------------------------------|

|                | 2004                                                |

| A              | APPROVED BY:                                        |

| John Hauser    | Veena Misra                                         |

| Jon-Paul Maria | Mehmet C. Öztűrk<br>Chair of the Advisory Committee |

#### **Biography**

Inkuk Kang was born on May 11, 1961 to Inseon Kang-Oh and Changhee Kang in Seoul, Korea. In 1981, he pursued his undergraduate studies at Kon-Kuk University. In May, 1985, he received his Bachelor of Science degree in Physics. After spending several years in military service and personal business, he came to US to study Physics in Stevens Institute of Technology in 1992. He received Master of Science in May, 1994. After spending another two years in the Physics department of the State University of New York at Buffalo, New York, he transferred to North Carolina State University to study electrical engineering in the field of microelectronics. In 2001, he joined Advanced Micro Devices, INC and expects to finish his Ph.D. degree at North Carolina State University in June, 2003.

## Acknowledgments

First of all, the author would like to express deep gratitude to Dr. Mehmet C. Öztürk, for his invaluable guidance, encouragement and help, in matters both technical and personal, during the entire course of this research. The author would also like to thank the other members of his advisory committee, Dr. John Hauser, Dr. Veena Misra, Dr. Dennis Maher and Dr. Gregory Parsons for their help and encouragement.

The author is also very grateful to former and current group members, Muhsin Celik, Patricia O'Neil, Ibrahim Ban, Nemanja Pesovic, Shyam Gannavaram, Jing Lue, Hongxiang Mo and Yanping Xu for their help and many sincere discussions. Special thanks are extended to Jin Min, Joongoo Hong, Sungkee Han, Indong Kim, Huicai Zhong, Greg Heuss, Heather Lazar, and Youseok Suh for their support and help.

The author wishes to thank AEMP microelectronics laboratory staff including Joan O'Sullivan, Harold Morton, Henry Taylor, Tina McNulty and Dr. Ginger Yu for their great support and timely help on various tools and experiments.

## **Table of Contents**

| Li | st of Figures                                                                 | vi    |

|----|-------------------------------------------------------------------------------|-------|

| I  | Introduction                                                                  | 1     |

|    | I.1 Source/Drain (S/D) Junction Requirements for Technology N                 | lodes |

|    | Beyond 50nm                                                                   | 1     |

|    | I.2 Selective Si <sub>1-x</sub> Ge <sub>x</sub> Source/Drain Technology       | 7     |

|    | I.3 Previous Work on Chemical Vapor Deposition of In-Situ Phosp               | horus |

|    | Doped Si                                                                      | 10    |

|    | a) Adsorption and Desorption of Phosphorus on Silicon                         | 11    |

|    | b) Deposition Rate                                                            | 14    |

|    | c) Phosphorus Incorporation during CVD of Si                                  | 14    |

|    | d) Phosphorus segregation                                                     | 17    |

|    | e) Phosphorus Incorporation in Si <sub>1-x</sub> Ge <sub>x</sub>              | 22    |

|    | I.4 Deposition System Used in This Work                                       | 23    |

|    | I.5 Surface Preparation Prior to Si <sub>1-x</sub> Ge <sub>x</sub> Deposition | 26    |

|    | I.6 Overview of Thesis                                                        | 28    |

|    | I.7 References                                                                | 28    |

| II | Deposition of In-situ Phosphorus Doped Silicon-Germanium Alloys               | 35    |

| 35 | II.1 Phosphorus Incorporation in Si <sub>1-x</sub> Ge <sub>x</sub>            | 35    |

|    | II.2 Growth Rate                                                              | 38    |

|    | II.3 Resistivity, Mobility and Carrier Concentration                          | 40    |

|    | II.4 Attempts to Increase the Phosphorus Incorporation                        | 50    |

|    | a) Effects of B <sub>2</sub> H <sub>6</sub> on Phosphorus Incorporation       | 52    |

|    | Effects of                                                                    | 54    |

|    | b) H <sub>2</sub> on Phosphorus Incorporation                                 | 54    |

|    | II.5 References                                                               | 58    |

| Ш  | I Flactrical Characterization of PN Junctions Formed Using In                 | _citu |

|    | Phosp        | phorus Doped Si <sub>1-x</sub> Ge <sub>x</sub>                                               | 61 |

|----|--------------|----------------------------------------------------------------------------------------------|----|

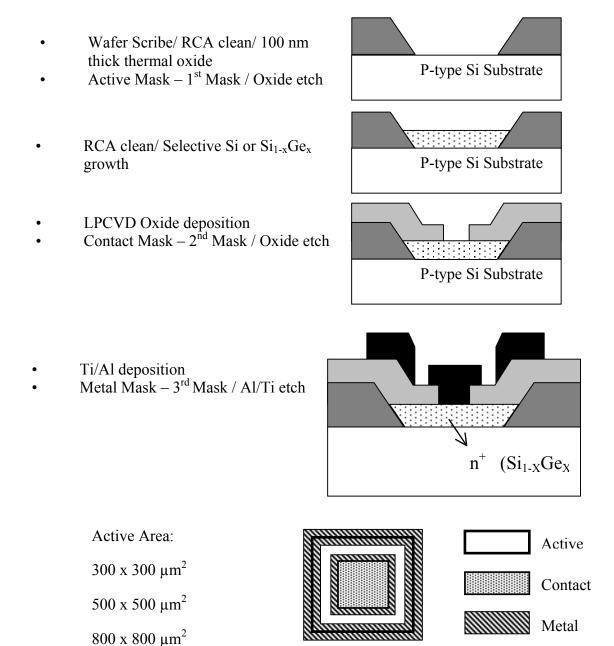

|    | III.1        | Diode Fabrication.                                                                           | 61 |

|    | III.2        | Leakage Current                                                                              | 63 |

|    |              | a) Junctions Fabricated on Lightly Doped Substrates                                          | 63 |

|    |              | b) Junctions Fabricated on Heavily Doped Substrates                                          | 69 |

|    | III.3        | Off-State Source/Drain leakage current for 45-22 nm technology                               |    |

|    | nc           | odes                                                                                         | 76 |

|    | III.4        | Junction Abruptness                                                                          | 79 |

|    | III.5        | References                                                                                   | 81 |

| IV | Select       | tive Deposition                                                                              | 82 |

|    | IV.1         | Introduction                                                                                 | 82 |

|    | IV.2         | Impact of Cl <sub>2</sub> on Selective Epitaxy of In-Situ Phosphorus Doped Si <sub>1</sub> . |    |

|    | $_{\rm x}$ C | Se <sub>x</sub>                                                                              | 83 |

|    |              | a) Selectivity and Growth Rate                                                               | 83 |

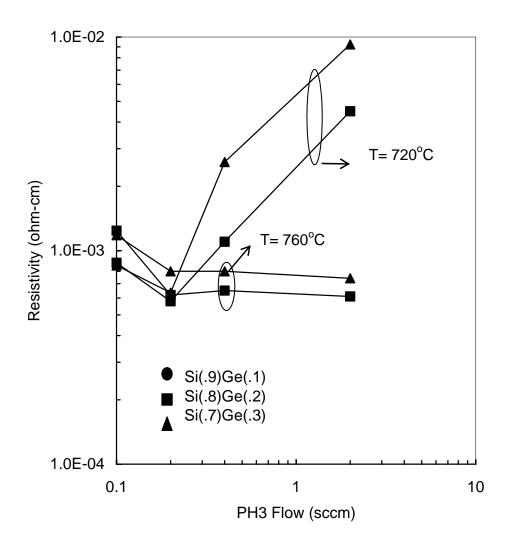

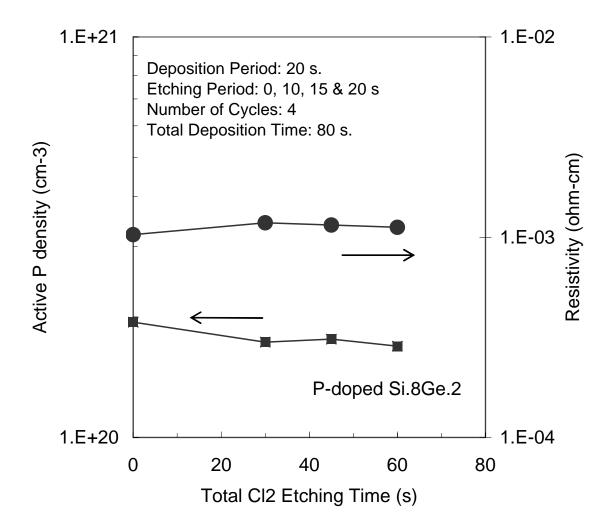

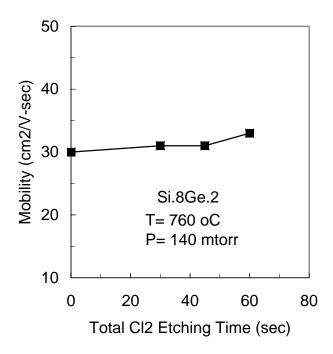

|    |              | b) Carrier concentration, resistivity and mobility                                           | 88 |

|    | IV.3         | Selective Si <sub>1-x</sub> Ge <sub>x</sub> Epitaxy Using Cycling                            | 91 |

|    | IV.4         | Conclusions                                                                                  | 97 |

| V  | Conc         | lusions and Future Work                                                                      | 99 |

|    |              |                                                                                              |    |

#### LIST OF FIGURES

| Figure I.1  | The schematic cross-sectional view of a source/drain region with associated series resistance components.                                                                                                                                                                                                   | 2  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure I.2  | Calculated sheet resistance using a resistivity of 4 – 6 x 10 <sup>-4</sup> ohmom and the maximum PMOS extension sheet resistance from ITRS2001.                                                                                                                                                            | 3  |

| Figure I.3  | Maximum allowable source/drain series resistance plotted as a function of MPU physical gate length (solid squares). Also shown is the contact resistance calculated using two different contact resistivities of 10 <sup>-7</sup> (open circles) and 10 <sup>-8</sup> ohm-cm <sup>2</sup> (open triangles). | 4  |

| Figure I.4  | Dependence of contact resistivity on carrier concentration and Schottky barrier height.                                                                                                                                                                                                                     | 6  |

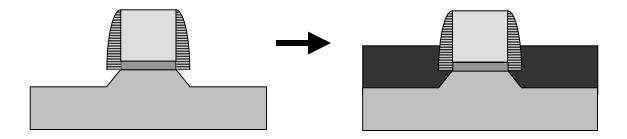

| Figure I.5  | Proposed method for fabricating junctions using the selective Si <sub>1-x</sub> Ge <sub>x</sub> technology                                                                                                                                                                                                  | 8  |

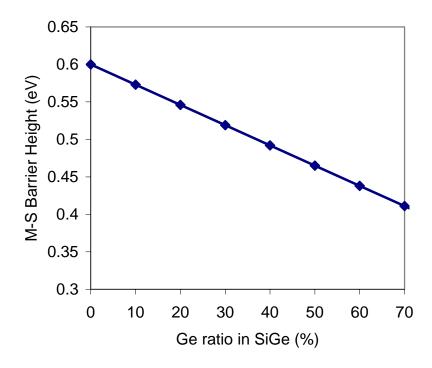

| Figure I.6  | Metal-Si (MS) contact barrier height using a mid-level metal                                                                                                                                                                                                                                                | 9  |

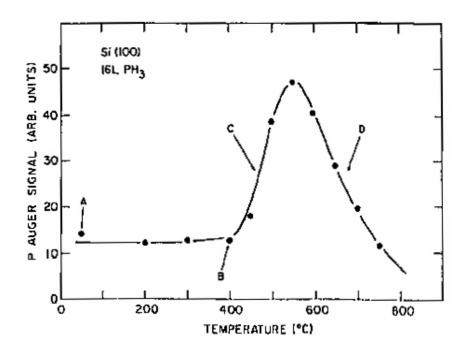

| Figure I.7  | Phosphorus Auger signal after flowing 1.6 x 10 <sup>-7</sup> Torr of PH <sub>3</sub> on (100) Si as a function of exposing temperature [15]                                                                                                                                                                 | 11 |

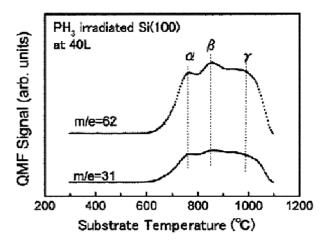

| Figure I.8  | Thermal desorption spectroscopy (TDS) spectra as a function of substrate temperature for P (m/e= 31) and $P_2$ (m/e= 62) at 40 L [17]                                                                                                                                                                       | 12 |

| Figure I.9  | Thermal desorption spectroscopy (TDS) spectra as a function of substrate temperature for P <sub>2</sub> for different PH <sub>3</sub> exposures [17]                                                                                                                                                        | 13 |

| Figure I.10 | Phosphorus profile in a multi-layer Si structure obtained by SIMS                                                                                                                                                                                                                                           | 15 |

| Figure I.11 | Phosphorus concentrations extracted from Figure I.10 at different PH <sub>3</sub> partial pressures.                                                                                                                                                                                                        | 16 |

| Figure I.12 | Phosphorus profile in a multi-layer Si structure obtained by SIMS                                                                                                                                                                                                                                           | 16 |

| Figure I.13 | Phosphorus concentrations extracted from Figure I.12 at different PH <sub>3</sub> partial pressures.                                                                                                                                                                                                        | 17 |

| Figure I.14 | Schematic view of surface and sub-surface state in Two State                                                                                                                                                                                                                                                |    |

|                | surface & surface, $E_d$ is the desorption energy, $E_b$ is the activation energy, and $E_s$ is the segregation (Gibb's free) energy.                                | 19 |

|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure I.15    | Calculated coulomb repulsion energy plotted as a function of dopant density.                                                                                         | 20 |

| Figure I.16    | Calculated coulomb repulsion energy plotted as a function of phosphorus doped film thickness                                                                         | 21 |

| Figure I.17    | Top view of the UHV-RTCVD System used in this work.                                                                                                                  | 25 |

| Figure I.18    | Deposition Chamber of the UHV-RTCVD Chamber consists of a quart dome with lamps on top of and around the dome                                                        | 26 |

| Figure II.1    | Phosphorus profiles of Si and Si <sub>1-x</sub> Ge <sub>x</sub> films obtained by SIMS                                                                               | 36 |

| Figure II.2 Si | and Si <sub>1-x</sub> Ge <sub>x</sub> growth rate with respect to inverse temperature                                                                                | 38 |

| Figure II.3    | Si <sub>1-x</sub> Ge <sub>x</sub> growth rate as a function of PH <sub>3</sub> flow at various temperatures.                                                         | 41 |

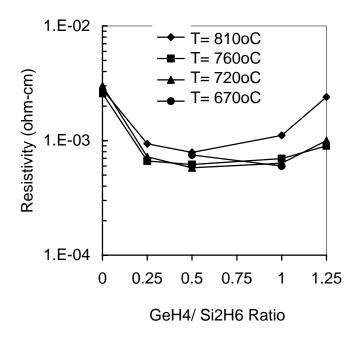

| Figure II.4 I  | Resistivity as a function of GeH <sub>4</sub> / Si <sub>2</sub> H <sub>6</sub> flow ratio at various temperatures.                                                   | 43 |

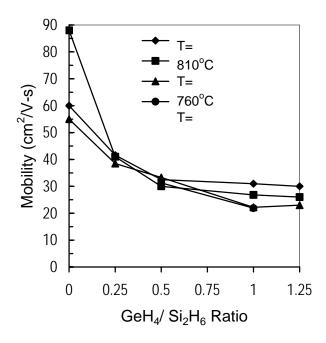

| Figure II.5    | Mobility as a function of GeH <sub>4</sub> / Si <sub>2</sub> H <sub>6</sub> flow ratio at various temperatures.                                                      | 44 |

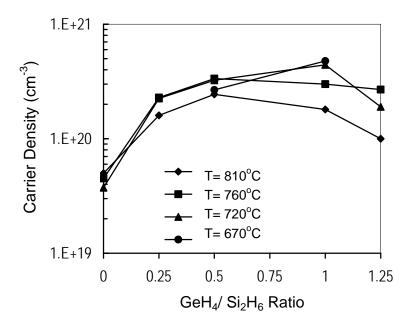

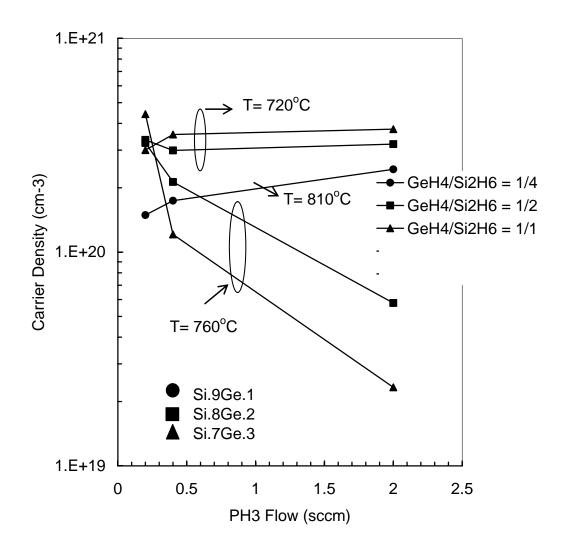

| Figure II.6    | Electrically active carrier density as a function of GeH <sub>4</sub> / Si <sub>2</sub> H <sub>6</sub> flow ratio at various temperatures.                           | 45 |

| Figure II.7    | Resistivity as a function of PH <sub>3</sub> flow.                                                                                                                   | 47 |

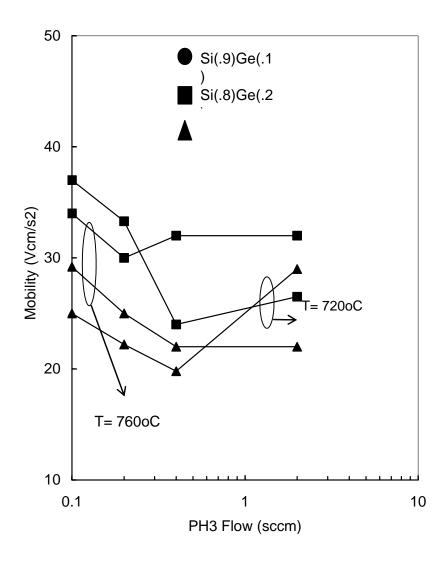

| Figure II.8    | Si <sub>1-x</sub> Ge <sub>x</sub> mobility as a function of the PH <sub>3</sub> flow                                                                                 | 48 |

| Figure II.9    | Active phosphorus density as a function of PH <sub>3</sub> flow at various temperatures.                                                                             | 50 |

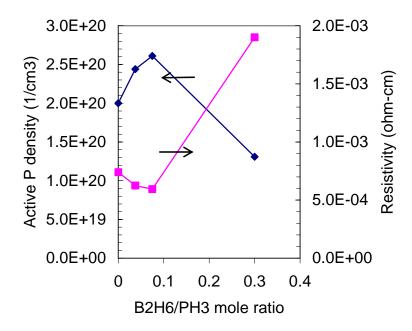

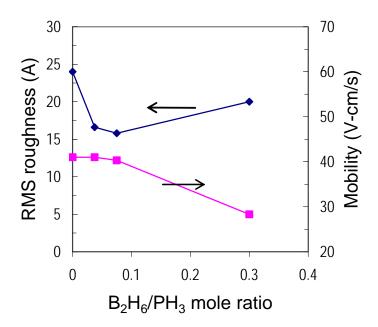

| Figure II.10   | Active P-density and resistivity as a function of the B <sub>2</sub> H <sub>6</sub> / PH <sub>3</sub> mole ratio.                                                    | 52 |

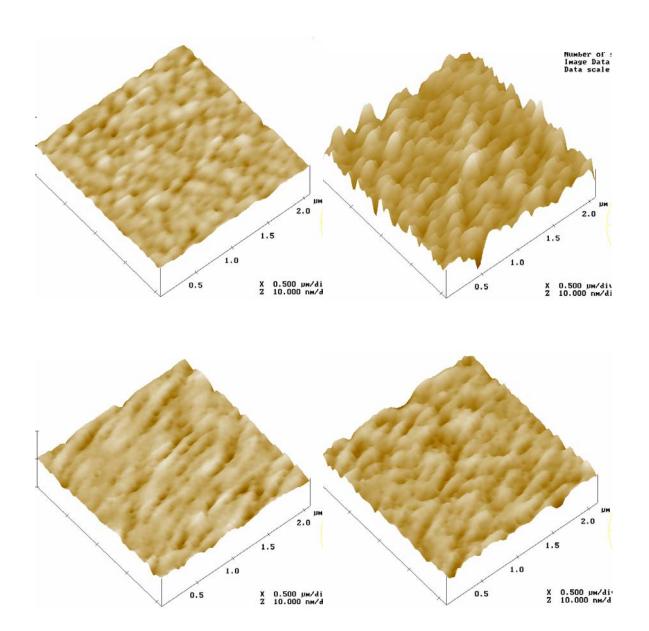

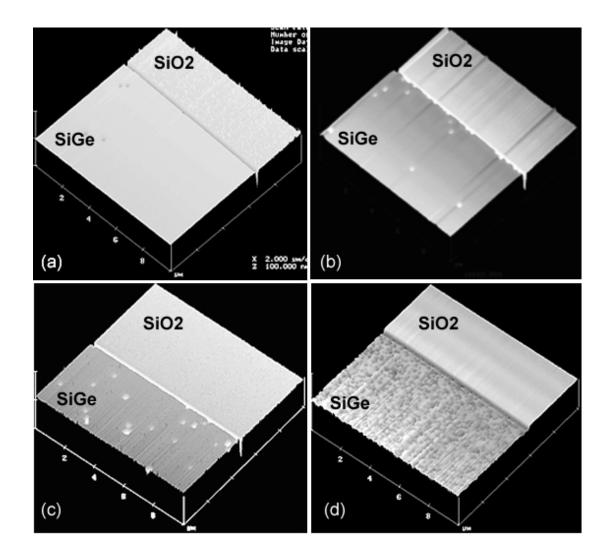

| Figure II.11   | AFM micrographs of Si <sub>1-x</sub> Ge <sub>x</sub> layers grown with B <sub>2</sub> H <sub>6</sub> flows of (a) 0 sccm, (b) 1 sccm, (c) 2 sccm, and (d) 10 sccm of | 53 |

| Figure II.12 F | RMS roughness and mobility as a function of B <sub>2</sub> H <sub>6</sub> /PH <sub>3</sub> mole ratio                                                                |    |

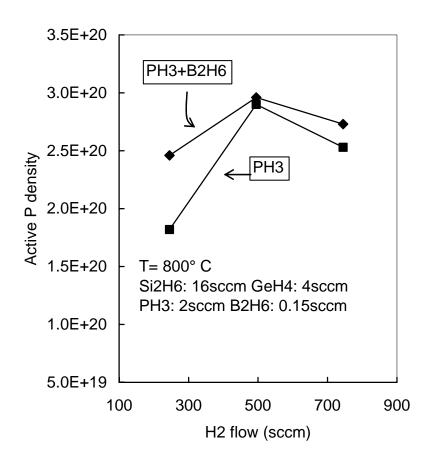

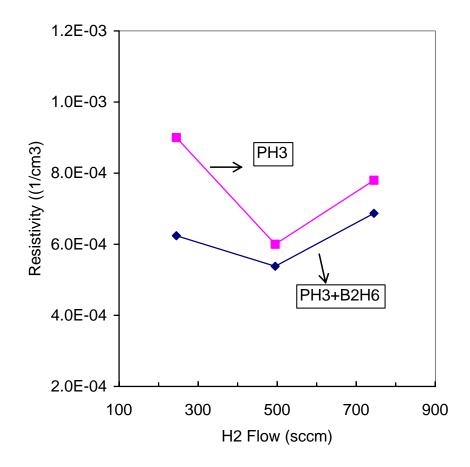

| Figure II.13  | Electrically active carrier density as a function of H <sub>2</sub> flow                                                                                                                                                                                                            | 55 |

|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure II.14  | Resistivity as a function of H <sub>2</sub> flow with and without B <sub>2</sub> H <sub>6</sub>                                                                                                                                                                                     | 56 |

| Figure III.1  | Diode Fabrication Steps                                                                                                                                                                                                                                                             | 62 |

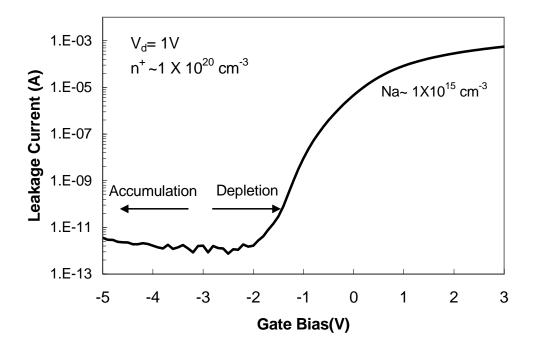

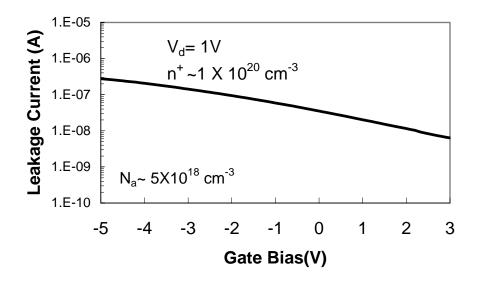

| Figure III.2  | Leakage current at 1V as a function of gate bias.                                                                                                                                                                                                                                   | 64 |

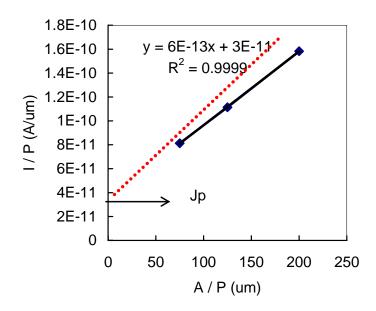

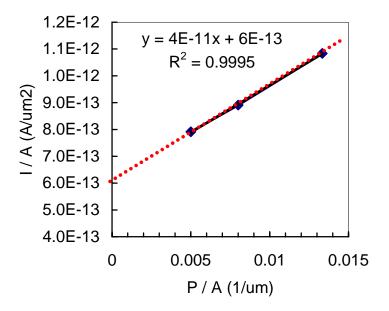

| Figure III.3  | Areal and peripheral leakage current density of the pn junction diodes.                                                                                                                                                                                                             | 65 |

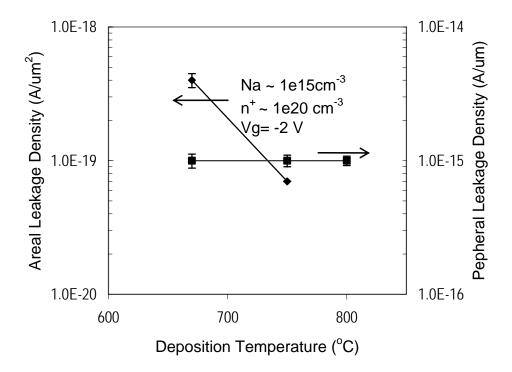

| Figure III.4  | Areal and peripheral components of the reverse leakage current as a function of the $Si_{1-x}Ge_x$ deposition temperature. The measurements were taken at a reverse bias of $1V$                                                                                                    | 66 |

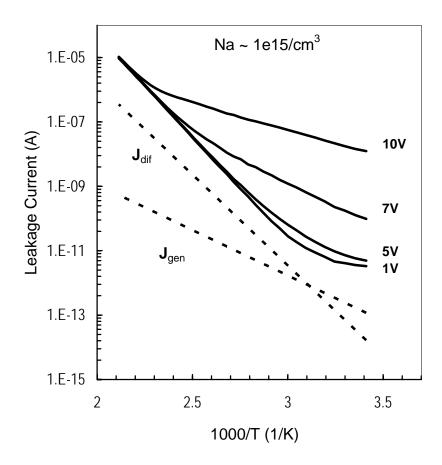

| Figure III.5  | Temperature dependence of leakage current on a low background doping.                                                                                                                                                                                                               | 68 |

| Figure III.6  | Leakage current at 1 V reverse bias plotted as a function of gate bias.                                                                                                                                                                                                             | 69 |

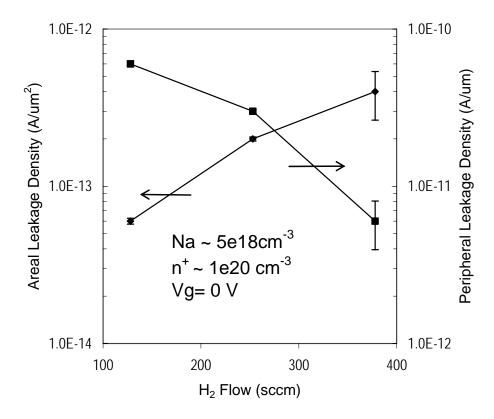

| Figure III.7  | Impact of $H_2$ addition to the areal and peripheral component of the reverse leakage current components of diodes fabricated on wafers with a high background doping density of (5 x $10^{18}$ cm <sup>-3</sup> ). The measurements were made at a reverse bias voltage of $1V$    | 70 |

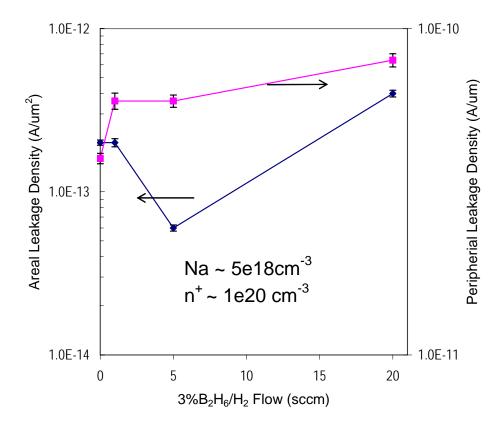

| Figure III.8  | Impact of $B_2H_6$ addition to the areal and peripheral component of the reverse leakage current components of diodes fabricated on wafers with a high background doping density of (5 x $10^{18}$ cm <sup>-3</sup> ). The measurements were made at a reverse bias voltage of $1V$ | 71 |

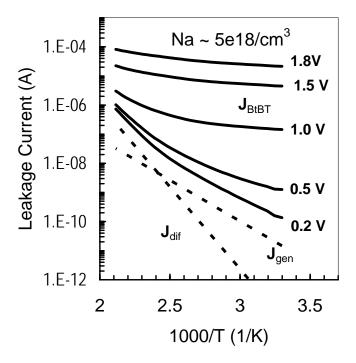

| Figure III.9  | Temperature dependence of the leakage current of diodes fabricates on wafers with a high background doping density                                                                                                                                                                  | 72 |

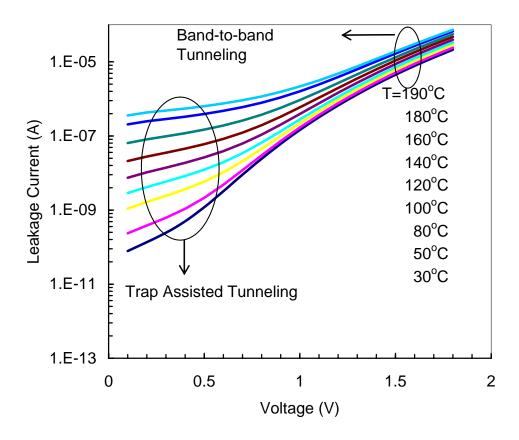

| Figure III.10 | Reverse current as a function of applied bias on a high background doping.                                                                                                                                                                                                          | 73 |

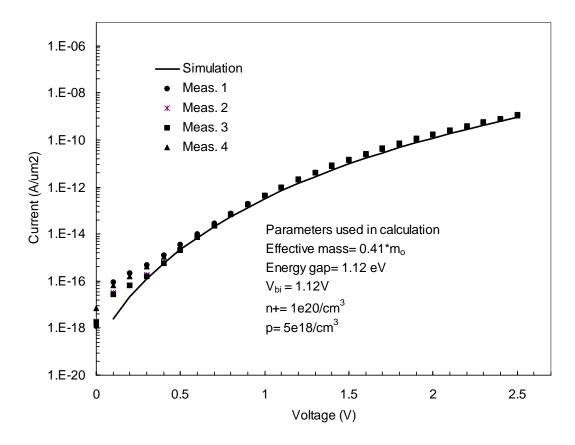

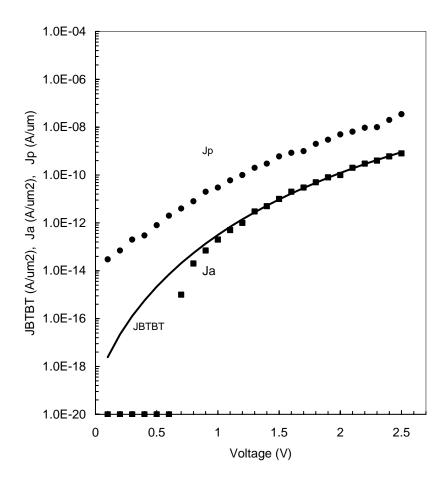

| Figure III.11 | Comparison between the calculated band-to-band tunneling current and the measured leakage current                                                                                                                                                                                   | 74 |

| Figure III.12 | Comparison between the calculated current and the areal and peripheral component from a measurement.                                                                                                                                                                                | 76 |

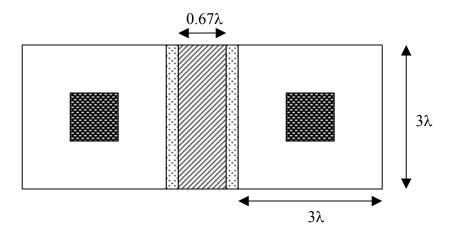

| Figure III.13 | $3\lambda$ design layout                                                                                                                                                                                                                                                            | 77 |

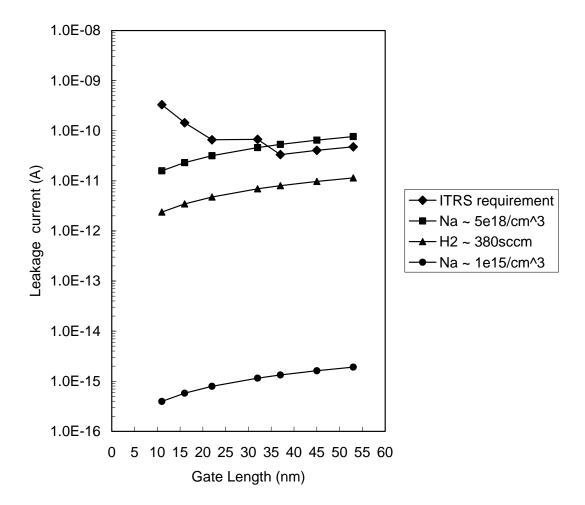

| Figure III.14 | ITRS 2001 requirements for sub-threshold leakage and extracted                                                                                                                                                                                                                      |    |

|               | values using areal and peripheral components of measured leakage currents.                                                                                                                                                            | 78 |

|---------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

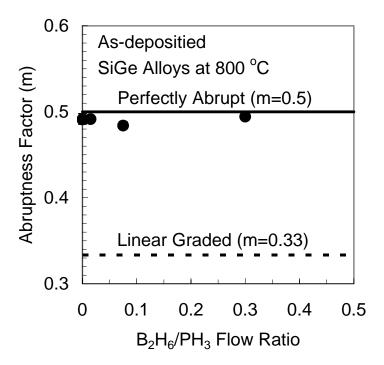

| Figure III.15 | Extracted phosphorus profile abruptness factors from reverse bias C-V measurements.                                                                                                                                                   | 79 |

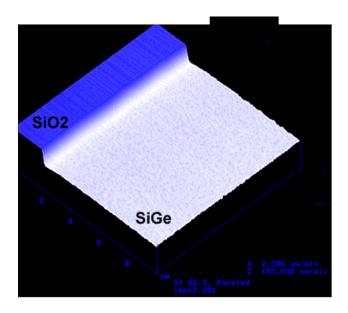

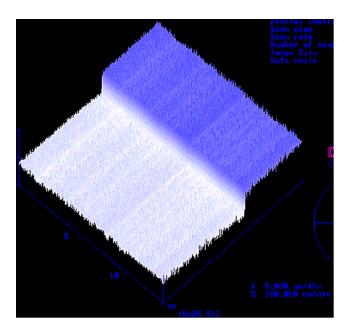

| Figure IV.1   | AFM image of selectively deposited in-situ P doped epitaxial Si <sub>1-x</sub> Ge <sub>x</sub> film. No nuclei are formed on the surrounding insulator surface.                                                                       | 84 |

| Figure IV.2   | AFM image of selectively deposited in-situ P doped epitaxial Si <sub>1-x</sub> Ge <sub>x</sub> film. Selectivity is lost and nuclei are formed on the surrounding insulator surface.                                                  | 84 |

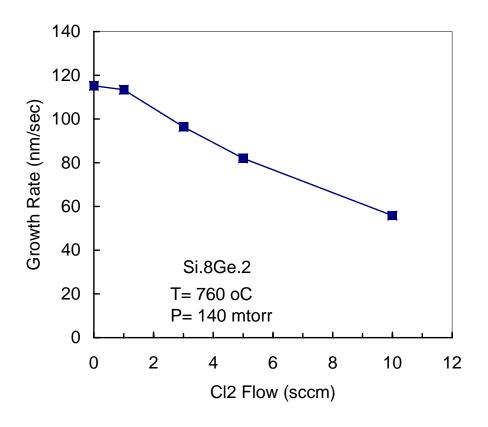

| Figure IV.3   | Effect of Cl <sub>2</sub> on Si <sub>1-x</sub> Ge <sub>x</sub> growth rate.                                                                                                                                                           | 85 |

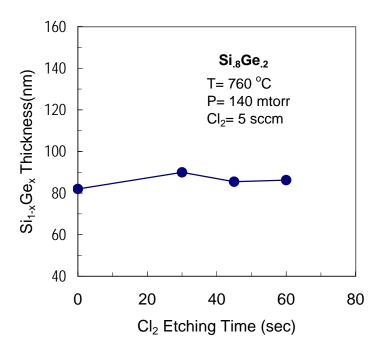

| Figure IV.4   | Si <sub>1-x</sub> Ge <sub>x</sub> Thickness as a function of Cl <sub>2</sub> etching time.                                                                                                                                            | 86 |

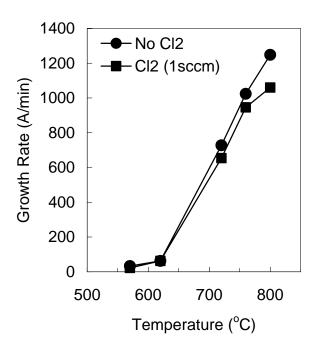

| Figure IV.5   | Growth rate of in-situ phosphorus doped Si <sub>1-x</sub> Ge <sub>x</sub> as a function of deposition temperature with and without Cl <sub>2</sub>                                                                                    | 88 |

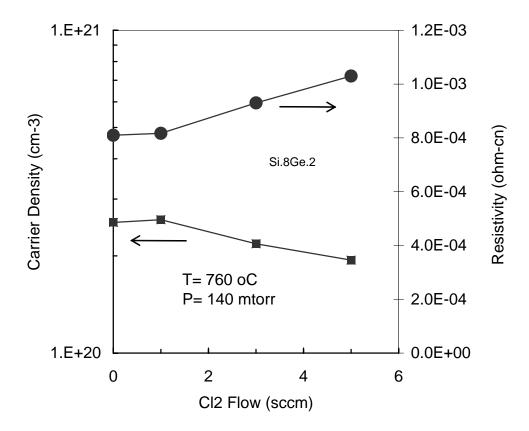

| Figure IV.6   | Active phosphorus concentration and Si <sub>1-x</sub> Ge <sub>x</sub> resistivity as a function of the Cl <sub>2</sub> flow rate                                                                                                      | 89 |

| Figure IV.7   | Hall mobility as a function of the Cl <sub>2</sub> flow rate.                                                                                                                                                                         | 90 |

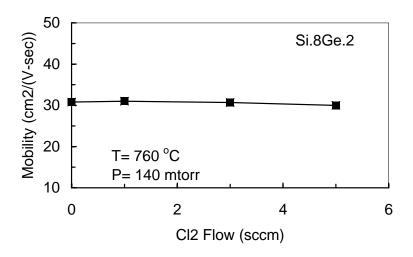

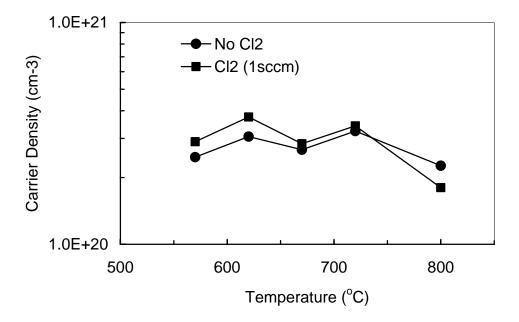

| Figure IV.8   | Active carrier concentration with and without Cl <sub>2</sub> at different temperatures.                                                                                                                                              | 90 |

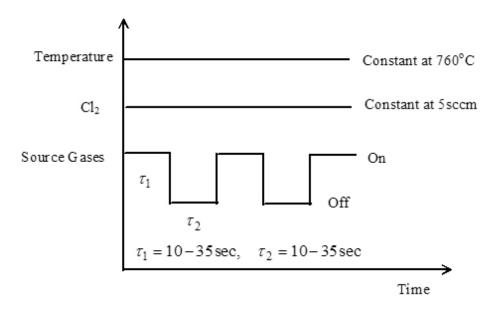

| Figure IV.9   | Cycling process used to improve the selectivity of in-situ phosphorus doped Si <sub>1-x</sub> Ge <sub>x</sub> layers.                                                                                                                 | 92 |

| Figure IV.10  | AFM images obtained from samples grown by the cycling method (a) (35 s deposition/35 s etch) – 2 cycles (b) (20 s deposit/20 s etch) - 5 cycles (c) (15 s deposition/15 s etch) – 4 cycles (d) (10 s deposition/10 s etch) – 7 cycles | 93 |

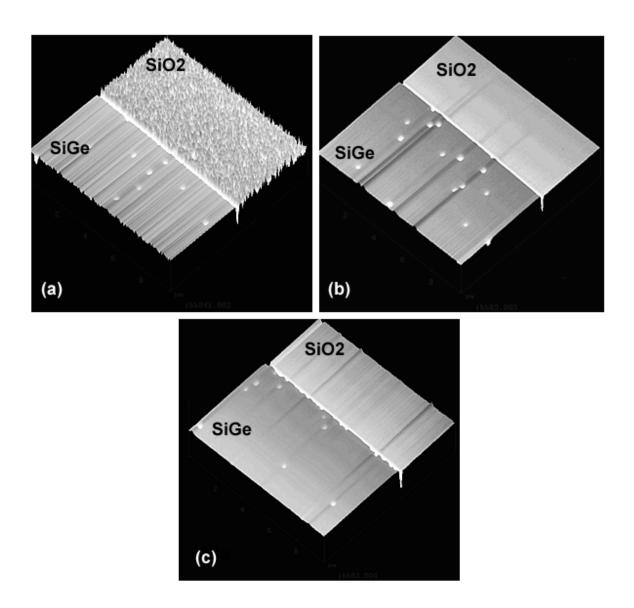

| Figure IV.11  | AFM images obtained from samples grown by the cycling method. (a) (20 sec. deposition / 10 sec. etch) – 4 cycles(b) (20 sec. deposition/ 15 sec. etch) – 4 cycles(c) (20 sec. deposition/ 20 sec. etch) – 4 cycles.                   | 95 |

| Figure IV.12  | Active phosphorus concentration and Si <sub>1-x</sub> Ge <sub>x</sub> resistivity obtained by cycling.                                                                                                                                | 96 |

| Figure IV 13  | Hall mobility as a function of etching time in samples grown by                                                                                                                                                                       |    |

| the cycling method. | .97 |

|---------------------|-----|

|---------------------|-----|

## I Introduction

This chapter begins with a summary of the source/drain engineering challenges for future CMOS technology nodes. This is followed by an overview of the Si<sub>1-x</sub>Ge<sub>x</sub> junction technology developed at NCSU prior to this work with emphasis on boron doped Si<sub>1-x</sub>Ge<sub>x</sub> junctions. Key findings from previously published work by other groups on deposition of heavily doped n+ Si and Si<sub>1-x</sub>Ge<sub>x</sub> layers is discussed as they relate to the work presented in this thesis. A description of he UHV-RTCVD system is provided along with details on sample preparation and film deposition.

## I.1 Source/Drain (S/D) Junction Requirements for Technology Nodes Beyond 50nm

In order to improve the performance of Complementary Metal Oxide Semiconductor (CMOS) integrated circuits, aggressive scaling of MOSFETs has been continued for the past 30 years. One of the key device parameters that needs to be scaled is the source/drain junction depth [1 - 3]. Currently used junction technologies rely on low-energy ion-implantation followed by rapid thermal annealing (RTA) [4]. However, as MOSFETs are scaled beyond the 50nm regime, this approach can no longer satisfy the source/drain requirements. According to the 2001 edition of the International Technology Roadmap for Semiconductors (ITRS), future junctions will require (a) junctions as shallow as 10 nm; (b) above equilibrium dopant activation; (c) super abrupt doping profiles; (d) contact resistivity near ~10<sup>-8</sup> ohm-cm<sup>2</sup> [5].

The main challenge in source/drain engineering is to form ultra-shallow junctions with a small parasitic series resistance. It is required that the total series resistance is limited to a small fraction of the channel 'on' resistance. In ITRS 1999, total series resistance was limited to 10% of the channel resistance [6]. In ITRS 2001, the percentage depends on the technology node and it varies from 17 % at 100 nm to 35 % at 22 nm.

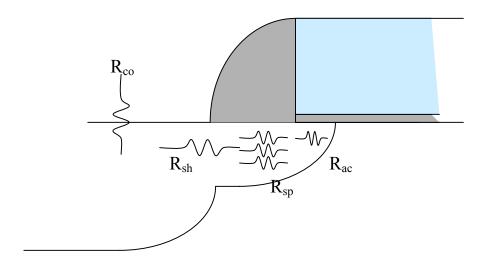

Figure I. 1 The schematic cross-sectional view of a source/drain region with associated series resistance components.

The total junction resistance, R<sub>i</sub>, can be modeled as:

$$R_{j} = R_{ac} + R_{sp} + R_{sh} + R_{co}, (1.1)$$

where  $R_{ac}$  is accumulation resistance,  $R_{sp}$  is spreading resistance,  $R_{sh}$  is sheet resistance of the junction under the sidewall spacer, and  $R_{co}$  is the contact resistance [2]. Shown in Figure I.1 is a cross-sectional view of a typical source/drain region illustrating these

components.  $R_{ac}$  (not shown in Figure I. 1) is the resistance of the tip of the extension under the gate. Its contribution to the total resistance is small compared to other components.  $R_{sp}$  is a strong function of the extension lateral doping gradient. MOSFETs at the end of the roadmap require lateral abruptness figures as small as 2nm/decade. Such values are impossible to achieve by techniques that involve thermal diffusion of dopants.  $R_{sh}$  is determined by the resistivity and the depth of the source/drain extension under the sidewall spacer.

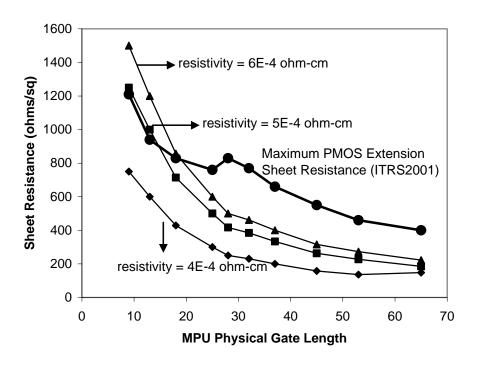

Figure I.2 Calculated sheet resistance using a resistivity of  $4 - 6 \times 10^{-4}$  ohm-cm and the maximum PMOS extension sheet resistance from ITRS2001.

Shown in Figure I.2 is the maximum allowable extension sheet resistance as a function of the MPU gate length for different technology nodes. Solid lines correspond to box profiles with different doping densities. As shown, a resistivity of 5 x  $10^{-4}$  ohm-cm is sufficient to satisfy the roadmap requirements for the extension resistance.

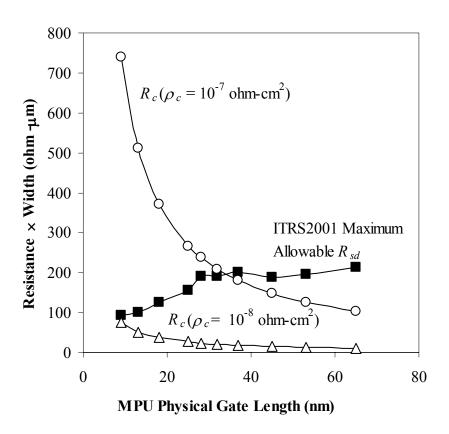

Figure I.3 Maximum allowable source/drain series resistance plotted as a function of MPU physical gate length (solid squares). Also shown is the contact resistance calculated using two different contact resistivities of 10<sup>-7</sup> (open circles) and 10<sup>-8</sup> ohm-cm<sup>2</sup> (open triangles).

Shown in Figure I.3 is the maximum allowable series resistance predicted in ITRS 2001 for different technology nodes. The maximum allowable series resistance is obtained

from the proposed values for the power supply voltage (V<sub>dd</sub>), drive current (I<sub>dd</sub>) and the parasitic S/D resistance percentage of the channel resistance ( $V_{dd}/I_{dd}$ ) given in ITRS 2001 [2]. Also plotted in Figure I.3 is the contact resistance for two specific contact resistivity values of  $10^{-7}$  and  $10^{-8}$  ohm-cm<sup>2</sup> calculated assuming the junction length is three times that of the physical gate length. As shown, if the contact resistivity is kept at its current value of ~ 10<sup>-7</sup> ohm-cm<sup>2</sup>, just the contact resistance alone will produce series resistance values that will be unacceptable for CMOS technology nodes with physical gate lengths smaller than ~ 30 nm. According to the ITRS 2001, future CMOS technology nodes will require contact resistivity values as low as 10<sup>-8</sup> ohm-cm<sup>2</sup>, as shown in Figure I.3. It is clear that such low contact resistivity values cannot be achieved on n<sup>+</sup> or p<sup>+</sup> Si using a single mid-gap contact material. In order to meet the contact resistivity requirements for future CMOS technology nodes, smaller contact barrier heights and/or above equilibrium dopant activation levels are required. This means that fundamentally new approaches will be required to decrease the contact resistivity by an order of magnitude during the next 10 years.

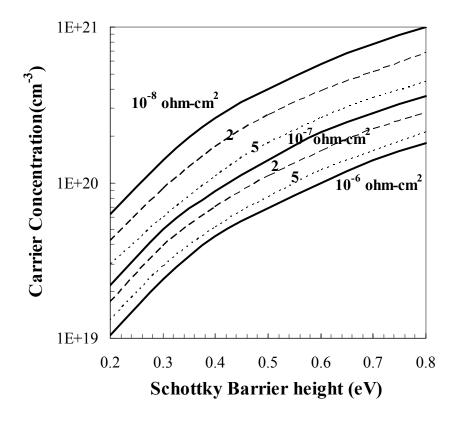

The resistivity of an ohmic contact is determined by the Schottky barrier height at the metal-semiconductor interface and the doping density under the metal as illustrated in Figure I.4. Due to Fermi level pinning, the Fermi level on the metal side lies near the Si midgap, which results in a contact barrier height of approximately  $E_g/2 \sim 0.6$  eV. Using this barrier height and the boron solid solubility limit of  $\sim 2 \times 10^{20}$  cm<sup>-3</sup> in Si, we obtain a contact resistivity of  $\sim 10^{-7}$  cm<sup>2</sup>, which is an order of magnitude higher than what we need at the end of the roadmap [7]. Since contact resistivity is an exponential function of the

barrier height, a large improvement in contact resistivity can be achieved by a small reduction in barrier height. For technology nodes beyond 50nm, ITRS 2001 predicts that the contact resistance will dominate the series resistance.

Figure I.4 Dependence of contact resistivity on carrier concentration and Schottky barrier height.

The source/drain challenges mentioned above are imposed by the fundamental limits of silicon, which requires new doping and contact formation technologies for future MOSFETs. A variety of junction formation methods are currently under investigation. Of these, laser thermal annealing of implanted dopants is standing out, and has been shown to

be capable of achieving abrupt profiles and above equilibrium dopant activation levels [8]. However, the technique results in metastable activation, which can be lost upon annealing at moderate temperatures. Furthermore, areas surrounding the junctions must be protected against melting with masking layers, which significantly adds to the process complexity. Much research needs to be carried out before the technology can be used in integrated circuit manufacturing.

#### I.2 Selective Si<sub>1-x</sub>Ge<sub>x</sub> Source/Drain Technology

Recently, a new junction formation technology based on selective deposition of insitu doped  $Si_{1-x}Ge_x$  alloys was proposed and demonstrated for  $p^+$ -n junctions using boron as the dopant [7]. In this technology, the source/drain regions are defined by isotropic etching and subsequently filled by selective  $Si_{1-x}Ge_x$  deposition. The etch depth determines the junction depth.

The objective of this thesis is to extend this concept to  $n^+$ -p junctions using phosphorus as the dopant. It is shown in this thesis that the method can meet all requirements of  $n^+$ -p junctions for future technology nodes. Shown in Figure I.5 are the basic fabrication steps for the proposed method for planar MOSFETs. The technology can also be used to form elevated junctions by depositing a  $Si_{1-x}Ge_x$  layer thicker than the etch depth. This provides a sacrificial layer to self-aligned contact formation via solid phase reactions between a metal and  $Si_{1-x}Ge_x$  [9 - 12]. This is one of the key challenges in forming reliable contacts to ultra-shallow junctions.

Isotropic Si-etch to form junction recess

- Selective Si-Ge Deposit

- In-situ above equilibrium doping

- Very abrupt doping gradient

- Low Temperature process

- Raised S/D MOSFET

Figure I.5 Proposed method for fabricating junctions using the selective Si<sub>1-x</sub>Ge<sub>x</sub> technology.

The advantages of the technology include:

- a) In-situ doping results in an abrupt doping profile since no thermal annealing is required to activate the dopants.

- b) Dopant activation in  $Si_{1-x}Ge_x$  is higher than it is in Si.

- c) Si<sub>1-x</sub>Ge<sub>x</sub> provides a smaller bandgap for low contact resistance.

- d) Low temperature (< 800°C) deposition provides compatibility with high-K dielectrics.

Figure I.6 Metal-Si (MS) contact barrier height using a mid-level metal.

There are several critical process integration issues, which needs to be taken into account. First and foremost, the etched region is required to reach the channel under the gate dielectric in other to realize the connection between the heavily doped junction and the channel. It has been suggested that some small distance can be tolerable without using a substantial increase in the series resistance [13]. Second, the etch chemistry has to be selective with respect to the gate dielectric. Finally, the surface should be suitable for Si<sub>1-x</sub>Ge<sub>x</sub> growth after etching. The very first advantage of Si<sub>1-x</sub>Ge<sub>x</sub> over Si is its smaller bandgap. Figure I.6 shows how the Ge content in Si<sub>1-x</sub>Ge<sub>x</sub> decreases the metal – Si barrier height assuming the Fermi level is pinned at the Si<sub>1-x</sub>Ge<sub>x</sub> midgap and the contact barrier

height is roughly equal to one half the semiconductor bandgap. It should be noted however that the figure can only provide an approximate guide since the  $Si_{1-x}Ge_x$  bandgap depends on the strain. To fully utilize the bandgap advantage of  $Si_{1-x}Ge_x$ , Ge concentration in the alloy must be raised preferably without forming misfit dislocations at the interface, which may lead to leaky junctions. However, with junction depths approaching a few nanometers, it will be easier to preserve the strain in the alloy.

## I.3 Previous Work on Chemical Vapor Deposition of In-Situ Phosphorus Doped Si

Chemical vapor deposition (CVD) of in-situ phosphorus and arsenic doped Si has been extensively studied by many research groups. The results show that unlike CVD of insitu boron doped Si, n-type doping presents unique challenges. Phosphorus atoms adsorbed on Si surface can reduce the number of available sites and result in significantly reduced growth rates. Another problem is that n-type dopants tend to segregate at the growth surface making it very difficult to grow heavily doped layers. Growing delta doped layers is also difficult due to the same reason.

In this section, we present a brief summary of previous work on CVD of in-situ phosphorus doped Si films. We begin with adsorption-desorption processes on Si and their impact on the deposition rate. We then discuss mechanisms responsible for surface segregation and its effect on phosphorus incorporation. We focus on phosphorus as the n-type dopant of interest.

Figure I.7 Phosphorus Auger signal after flowing 1.6 x 10<sup>-7</sup> Torr of PH<sub>3</sub> on (100) Si as a function of exposing temperature [15].

#### a) Adsorption and Desorption of Phosphorus on Silicon

Yu and Meyerson studied adsorption and desorption of PH<sub>3</sub> on (100) Si [14, 15]. Figure I.7 shows the phosphorus Auger signal after flowing 1.6 x  $10^{-7}$  Torr-sec of PH<sub>3</sub> on (100) Si at various temperatures [15]. As shown, PH<sub>3</sub> readily adsorbs on the Si surface associatively even at room temperature and the phosphorus level stays constant up to  $400^{\circ}$ C (A  $\rightarrow$  B). The phosphorus signal starts to rise rapidly above  $400^{\circ}$ C and reaches a maximum at 550°C due to hydrogen desorption, which provides more available sites to phosphorus atoms (B  $\rightarrow$  C  $\rightarrow$  Max. at 550°C). Over 550°C, phosphorus starts to desorb and phosphorus coverage of the surface decreases (D).

Figure I.8 Thermal desorption spectroscopy (TDS) spectra as a function of substrate temperature for P (m/e= 31) and  $P_2$  (m/e= 62) at 40 L [17].

Hirose and Sakamoto studied phosphorus desorption from Si using thermal desorption spectroscopy (TDS) [16]. After exposing (100) Si surface to 40 langmuirs (1 langmuir = 1 x  $10^{-6}$  Torr-sec) of PH<sub>3</sub> at 600°C, the detected desorption species were P<sub>2</sub> (mass number, m/e=62) and P (m/e=31) only and the P signal was mainly from ionization of P<sub>2</sub> in the quadruple mass filter (QMF) as shown in Figure I.8. Based on this finding, they concluded that desorbed species are mostly P-P. Figure I.9 shows the P<sub>2</sub> signal with three peaks  $\alpha$ ,  $\beta$ , and  $\gamma$  at 750, 850, and 1000°C, respectively. For low PH<sub>3</sub> exposure, only the  $\beta$  peak exists and it shifts to higher temperatures as the phosphine exposure is reduced. Hirose and Sakamoto claim that the  $\beta$  peak is the desorption of P<sub>2</sub> following the reactions:

2 Si-P (Migrating hetero-dimers)  $\rightarrow$  2 Si + 2 P (migration)  $\rightarrow$  P<sub>2</sub>

and  $\alpha$  peak is the direct desorption of P<sub>2</sub> as

P-P (Migrating mono-dimer)  $\rightarrow$  2 P (migration)  $\rightarrow$  P<sub>2</sub>.

Figure I.9 Thermal desorption spectroscopy (TDS) spectra as a function of substrate temperature for  $P_2$  for different  $PH_3$  exposures [17].

Their arguments are well supported by scanning tunneling microscopy (STM) or Fourier transform infrared spectroscopy (FTIR) studies [17 - 21]. Phosphorus atoms mostly form P-Si hetero-dimers for low exposures of PH<sub>3</sub>, and Si-P and P-P dimers for high PH<sub>3</sub> flows.

#### b) Deposition Rate

Growth rate reduction for gas source molecular beam epitaxy (GS-MBE) or ultrahigh vacuum chemical vapor deposition (UHV- CVD) of silicon with in-situ P or As doping using PH<sub>3</sub> or AsH<sub>3</sub> is well established [22 - 29]. It has been shown that phosphorus atoms passivate the Si surface and block adsorption sites for Si precursors such as SiH<sub>4</sub> or Si<sub>2</sub>H<sub>6</sub>, which results in reduced growth rates. Soares et.al. claim that each surface arsenic atom has a lone pair of electrons instead of a dangling bond since an As atom has one more electron than a Si atom [29]. They claim that a Si-As dimer acts as if it has a single dangling bond. It has been reported that the overall activation energy of silane decomposition increases from  $\sim$  10 kcal/mol without arsine to  $\sim$  40 kcal/mol with arsine [30]. Farrow and Filby concluded that arsine acts as a poison in silane pyrolysis deactivating the adsorption sites [31]. J. Shan et.al. have observed that surface phosphorus atoms can form PSiH "hydrided heterodimers" in the presence of surface hydrogen. PSiH has stronger Si-H bonding energy than Si-SiH does, which can degrade the Si growth [21].

#### c) Phosphorus Incorporation during CVD of Si

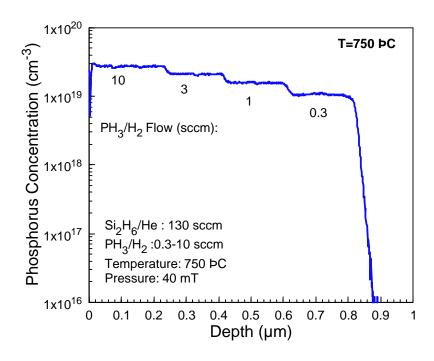

Shown in Figure I.10 is the phosphorus concentration in a multi-layer Si epitaxial structure grown by UHV-RTCVD at NC State University by Ibrahim Ban [27]. The profile was obtained by secondary ion mass spectroscopy (SIMS). Different doping levels were obtained by changing 50 ppm PH<sub>3</sub> flow (diluted in H<sub>2</sub>) between 0.3 and 10 sccm. The silicon precursor was 10% Si<sub>2</sub>H<sub>6</sub> diluted in He and its flow was kept constant at 130 sccm.

Figure I.10 Phosphorus profile in a multi-layer Si structure obtained by SIMS.

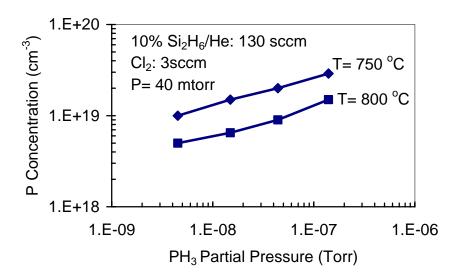

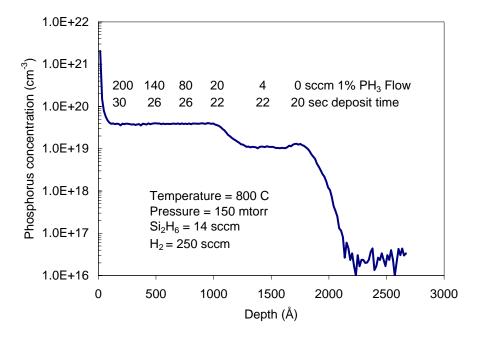

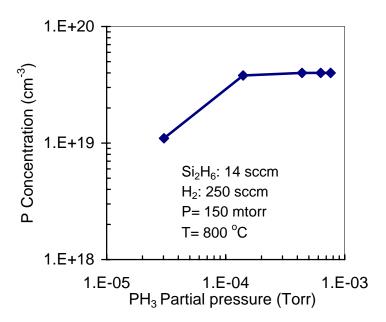

Each step in Figure I.10 corresponds to a growth cycle of one minute at 750 °C, except for the last layer (10 sccm case) which was grown for 1.5 min. Figure I.11 shows the phosphorus levels observed in Figure I.10 as a function of the PH<sub>3</sub> partial pressure. Under these conditions, the phosphorus level increases monotonically with the PH<sub>3</sub> partial pressure in the growth ambient [27]. Figure I.12 shows another SIMS multi-layer profile obtained by depositing the layers at 800°C and 150 mtorr. In an attempt to increase the P incorporation, PH<sub>3</sub> dilution in H<sub>2</sub> was changed from 50 ppm to 1 %. PH<sub>3</sub> flows of 0, 4, 20, 80, 140, and 200 sccm were used to obtain a multi-layer structure. As shown, phosphorus incorporation saturates above a PH<sub>3</sub> flow of approximately 20 sccm.

Figure I.11 Phosphorus concentrations extracted from Figure I. at different PH<sub>3</sub> partial pressures.

Figure I.12 Phosphorus profile in a multi-layer Si structure obtained by SIMS.

Figure I.13 Phosphorus concentrations extracted from Figure I. at different PH<sub>3</sub> partial pressures.

As shown in Figure I.13, at higher  $PH_3$  partial pressures (three orders of magnitude higher), phosphorus concentration saturates at around 4 x  $10^{19}$  cm<sup>-3</sup>.

Similar behavior has been observed by others [22, 23, 25, 28 - 32]. While P-P desorption is enhanced when PH<sub>3</sub> partial pressure is increased, it can not fully explain saturation of phosphorus concentration. Instead, segregation coupled with coulomb repulsion has been proposed to explain this phenomenon.

#### d) Phosphorus segregation

Surface segregation of n-type dopants, including As [33], P [34 - 38], and Sb [39 -

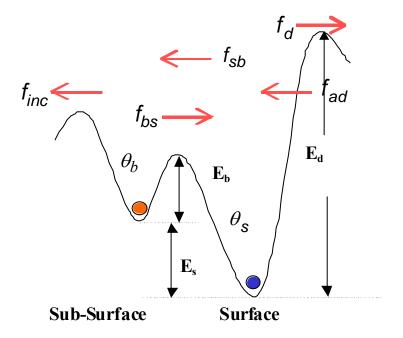

47] has been extensively studied by different groups. H. Jorke proposed a two state model to explain the phosphorus segregation [48]. Using rate equations he examined the subsurface and surface states at the growing boundary. Shown in Figure I.14 is the energy diagram used in the two-state model. On this figure,  $\theta_b$  and  $\theta_s$  are the percent coverages of the dopant atoms at the sub-surface and surface, E<sub>d</sub> is the desorption energy, E<sub>b</sub> is the activation energy for segregation, and E<sub>s</sub> is the segregation (Gibb's free) energy. Two atoms, A and B referred to as sub-surface and surface atoms take part in the exchange mechanism. In this model, the critical energies are the desorption energy, E<sub>d</sub>, activation energy for segregation, E<sub>b</sub> and the segregation energy, E<sub>s</sub>. During the formation of a monolayer, a phosphorus atom (A) at the sub-surface exchanges its position with a surface Si atom (B). The driving force for this exchange originates from the difference in the bonding energies of Si – P and Si – Si bonds [46]. The difference is Gibb's free energy or the segregation energy, E<sub>s</sub>. For this exchange to occur the sub-surface phosphorus atom should overcome the activation barrier energy, E<sub>b</sub>. The segregation probability can be expressed as:

$$P = \exp(-E_s / kT) \tag{1.1}$$

Gibb's energies for P, As, and Sb are known as around 0.63, 0.8, and 1.2 eV, respectively [34, 35, 37, 49].

Figure I.14 Schematic view of surface and sub-surface state in Two State Model, where  $\theta_b$  and  $\theta_s$  are the dopant coverages at the sub-surface & surface,  $E_d$  is the desorption energy,  $E_b$  is the activation energy, and  $E_s$  is the segregation (Gibb's free) energy.

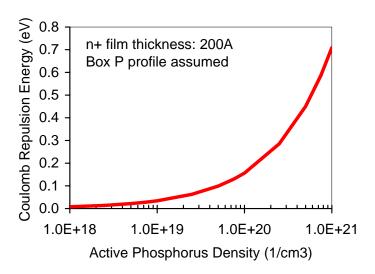

Another phenomenon that should be taken into account is Coulomb repulsion. During in-situ doping, large numbers of Si-P or Ge-P heterodimers exist on the surface. When a Si or Ge atom is adsorbed on a surface phosphorus atom, the phosphorus atom becomes electrically active. A coulomb repulsive force is applied to the ionized and positively charged phosphorus atom by the other, previously incorporated positively charged phosphorus atoms in the deposited film. The coulomb repulsion energy,  $E_i^{coul}$  for an incorporated phosphorus atom at layer "i" is given by

$$E_i^{Coul} = \frac{q}{2\varepsilon} \sum_{j=1,2...}^i \sigma_j \lambda_j \exp(-x_{ij}/\lambda_j), \qquad (1.2)$$

where  $\sigma_j$  is the conductivity and  $\lambda_j$  is the screeening length at  $j^{th}$  plane defined as,

$$\lambda_{j} = \frac{2\pi\varepsilon \hbar^{2}}{m^{*}q^{2}} \left(\frac{1}{3}\pi\right)^{1/6} \left(n_{j} \frac{4\pi\varepsilon \hbar^{2}}{m^{*}q^{2}}\right)^{-1/6}, \tag{1.3}$$

where  $x_{ij}$  is the distance between "i" and "j" planes,  $\varepsilon = \varepsilon_0$  x 11.8 for Si,  $m^*$  is the effective mass, and  $n_j$  is the carrier density at layer j. By using a phosphorus box profile in the Si layer,  $\lambda_1 = \lambda_2 = \ldots = \lambda_j$  and  $\sigma_1 = \sigma_2 \ldots = \sigma_j$  are assumed in equations 1.2 and 1.3.

Figure I.15 Calculated coulomb repulsion energy plotted as a function of dopant density.

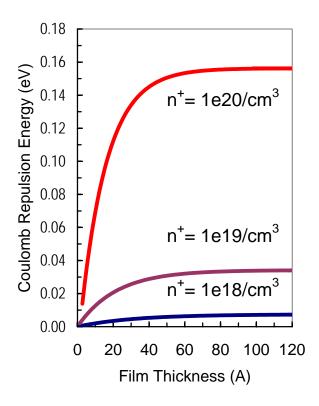

Figure I.16 Calculated coulomb repulsion energy plotted as a function of phosphorus doped film thickness

At i = 150 (total layer thickness  $\sim$  200 Å), the calculated coulomb repulsion energy is shown in Figure I.15. It can be observed that as the doping level is increased, the repulsion energy increases exponentially. In Figure I.15, the Coulomb repulsion energy at  $n=1 \times 10^{21} cm^{-3}$  is around 0.71 eV, which is higher than the reported segregation energy resulting from the difference in bonding energies of Si-P and Si-Si. Figure I.16 shows the Coulomb repulsion as a function of the phosphorus doped film thickness. As shown, the accumulated repulsion energy sharply increases with thickness and levels off above a critical thickness due to charge screening. Consequently, the contribution of the repulsion

energy from an initial layer to the surface layer becomes negligible. In summary, the strong coulomb repulsion enhances phosphorus segregation, limiting phosphorus incorporation in the deposited layer.

Since segregation is a thermally activated process, deposition at very low temperatures (~ 250°C or less) can yield films with high phosphorus levels. Using Photo-CVD, a phosphorus level near 1 x 10<sup>21</sup> cm-3 was obtained at 250°C [50]. Nützel and Abstreither observed that while segregation still exists at temperatures as low as 300°C segregation length begins to decrease exponentially at 500°C [49]. The segregation length was measured from the phosphorus tale in undoped Si layer, which was grown on a phosphorus covered Si surface. They also reported that antimony segregation lengths are 35, 18, 11 and 6nm for undoped Si growth rates of 0.36, 1.2, 3.6 and 12 nm/min, respectively. Thus, lower growth rates can result in enhanced segregation.

#### e) Phosphorus Incorporation in Si<sub>1-x</sub>Ge<sub>x</sub>

By introducing germane to the deposition chemistry, phosphorus incorporation is greatly enhanced and the Si<sub>1-x</sub>Ge<sub>x</sub> growth is not degraded as the phosphine flow is increased. Jang, Liao, and Reif reported an order of magnitude higher phosphorus incorporation and six times higher growth rate in Si<sub>1-x</sub>Ge<sub>x</sub> with a Ge content of 20% [23]. They proposed that P-P dimerization is retarded by the presence of Ge ad-atoms on the surface. Since the Ge-P bond is weaker than the Si-P bond, phosphorus desorption is enhanced, which increases the number of available sites for adsorption and enhances the growth rate.

Enhanced phosphorus incorporation in Si<sub>1-x</sub>Ge<sub>x</sub> may come from a higher density of monatomic phosphorus atoms on the surface, which results in retarded phosphorus segregation. As discussed before, P-P dimers are easily desorbed or segregated. Nützel et al reported that phosphorus segregation lengths are 300, 100, 40 and 4 nm in 0, 3, 7 and 20 % of Ge in Si<sub>1-x</sub>Ge<sub>x</sub>, respectively [52]. The films were grown at 490°C using MBE. For 20 % Ge in Si<sub>1-x</sub>Ge<sub>x</sub>, the segregation length is reduced by nearly two orders of magnitude. They proposed that reduced segregation comes from the competition between P and Ge atoms although the germanium segregation lengths are significantly lower than those of phosphorus. Unfortunately too much germane can also degrade phosphorus incorporation. Xie et.al. also reported that the presence of Ge surface atoms can degrade phosphorus incorporation due to the enhanced P desorption in the form of Ge-P heterodimers [28].

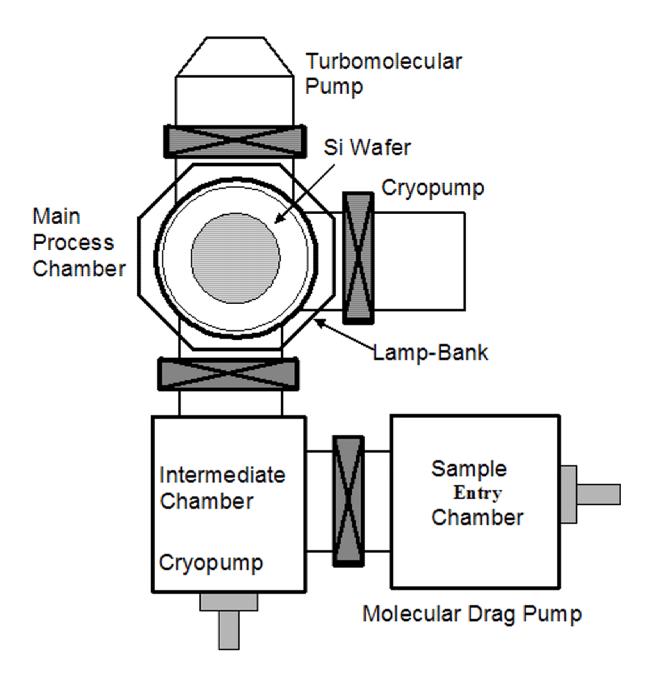

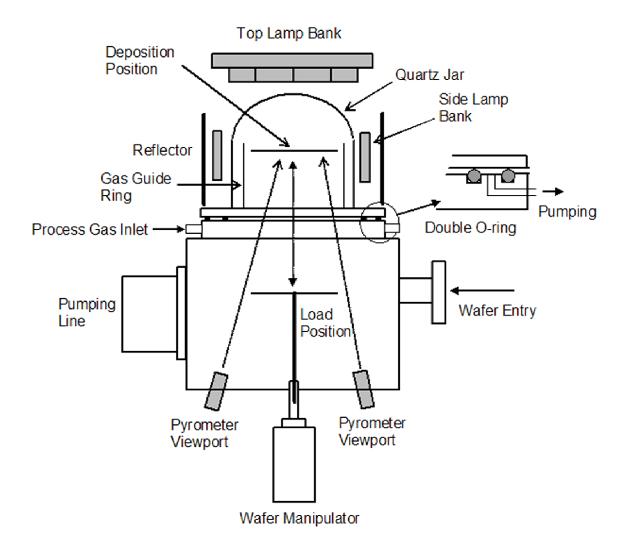

## I.4 Deposition System Used in This Work

In this work, in-situ phosphorus doped Si and Si<sub>1-x</sub>Ge<sub>x</sub> alloys were deposited in an Ultra-High Vacuum Rapid Thermal Chemical Vapor Deposition (UHV-RTCVD) reactor shown in Figure I.17. The system is capable of processing both 6" and 8" wafers. The system was designed and built at North Carolina State University. Construction of this system was accomplished as part of this thesis jointly with Dr. Nemanja Pesovic, who was also a graduate student in my research group. The system consists of three separate chambers: a load-lock (sample entry chamber), an intermediate chamber, and a main process chamber. The load lock is pumped by a dry molecular drag pump to a base pressure of 10<sup>-5</sup> Torr. The intermediate chamber serves as a vacuum buffer between the

sample entry and main process chambers and it is pumped by a cryopump to a base pressure of  $10^{-9}$  Torr. Another cryopump maintains a base pressure of  $10^{-9}$  Torr in the main chamber. During growth, a turbomolecular/molecular-drag combination pump backed up by a dry mechanical pump is used. All pumps and gate valves on the system are oil-free to minimize hydrocarbon contamination. The main chamber is double walled (circulated with oil to heat up the chamber) stainless steel chamber with a quartz dome on top. Under the quartz dome, the seal consists of two o-rings with differential pumping between the O-rings by a small turbomolecular pump to maintain a pressure of  $\sim 10^{-6}$  Torr. The wafer is heated through the quartz dome by tungsten-halogen lamps on top and around the dome. Two optical pyrometers ( $\lambda = 4.9 - 5.3 \ \mu m$ ) focused at the edge and center of the wafer are used the measure the wafer temperature. The pyrometer focused at the wafer center is used in a closed-loop feedback control system. The wafer transfer mechanism was designed to load five wafers at a time. Figure I.18 is the detailed cross-sectional view of the main process chamber.

Figure I.17 Top view of the UHV-RTCVD System used in this work.

Figure I.18 Deposition Chamber of the UHV-RTCVD Chamber consists of a quart dome with lamps on top of and around the dome.

# I.5 Surface Preparation Prior to Si<sub>1-x</sub>Ge<sub>x</sub> Deposition

Wafers were cleaned *ex-situ* using a standard RCA clean (SC1/SC2). Immediately before loading into the system, the wafers were dipped in a 1 % HF solution for 30 seconds followed by a rinse in deionized water for 15 seconds. The purpose of the HF dip is to

remove protective oxide grown during RCA clean. In addition, hydrogen passivates the Si dangling bonds to protect against contamination.

After the HF dip, a wafer cassette containing five wafers is loaded into the load-lock. The procedure for transferring a wafer to the deposition chamber is as follows: Queue time before loading the wafer cassette into the vacuum chamber was 10 - 15 min. After reaching a pressure of  $10^{-5}$  Torr in the load-lock, the wafer cassette is transferred into the intermediate chamber, which can be pumped down to  $10^{-7}$  Torr in a few minutes by the cryopump. After reaching  $10^{-8}$  Torr a single wafer from the cassette is transferred to the main chamber. The main chamber is first pumped by the cryopump. Upon reaching the base pressure a gate valve isolates the cryopump and the chamber is switched to the turbomolecular/molecular drag combination pump used to pump the process gasses.

An *in-situ* vacuum bake was performed at 800°C for 10-15 seconds to remove any residual oxygen and carbon on the wafer surface. Under ultra-high vacuum, it has been reported that 800°C, 10 s is enough to reduce the oxygen below the SIMS detection level and the carbon level below  $\sim 10^{18}$  cm<sup>-3</sup> [53, 54]. Epitaxial growth is initiated by gas switching and terminated by both gas and temperature switching.

Gases used in this work were 100% Si<sub>2</sub>H<sub>6</sub>, 10% GeH<sub>4</sub> mixed with H<sub>2</sub>, 1% PH<sub>3</sub> mixed with H<sub>2</sub>, and 100% H<sub>2</sub>.

## I.6 Overview of Thesis

The experimental work carried out during the course of this research has been summarized in three chapters. Electrical and structural properties of the deposited layers can be found in Chapter II. In these experiments, Hall Effect measurements were heavily relied on to determine the active carrier concentration in the grown layers as well as film resistivity and carrier mobility. Chapter III provides a detailed account of the properties of diodes fabricated using the in-situ doped layers. The emphasis in Chapter III is on the reverse leakage current and different mechanisms that contribute to the overall junction leakage. Chapter IV focuses on selective deposition and methods to improve the process selectivity.

#### I.7 References

- Y. Taur, D.A. Buchanan, W. Chen, D.J. Frank, K.E. Ismail, S. Lo, G.A. Sai-Halasz,

R.G. Viswanathan, H.C. Wann, S.J. Wind, and H. Wong, "CMOS Scaling into the Nanometer Regime", Proceeding of IEEE, V85, NO 4, pp. 486-504, 1997

- 2. K. K. NG and W. T. Lynch, The impact of intrinsic series resistance on MOSFET scaling, IEEE Trans. Electron Devices 34, 503-511 (1987)

- Y. Yaur, Y. –J. Mii, D. J. Frank, H. –S. Wong, D. A. Buchanan, S. J. Wind, S. A. Rishton, G. A. Sai-Halasz, and E. J. Nowak, CMOS scaling into the 21<sup>st</sup> century:

um and beyond, IBM J. RES. DEVELOP. V39, 245-260 (1995)

- 4. C. R. Cleavelin, B. C. Covington, and L. A. Larson, Front end of line

- considerations for progression beyond the 100 nm node ultrashallow junction requirements, J. Vac. Sci. Technol. B 18, 346 353 (2000)

- 5. International Technology Roadmap for Semiconductors (SIA, San Jose, CA), 2001

- 6. International Technology Roadmap for Semiconductors (SIA, San Jose, CA), 1999

- 7. S. Gannavaram, N. Pesovic and M. C. Öztürk, Low Temperature (<800°C) Recessed Junction Selective Silicon-Germanium Source/Drain Technology for sub-70 nm CMOS, International Electron Devices Meeting 2000, Technical Digest

- S. Talwar, Y. Wang, and C. Gelatos, Laser thermal processing (LTP) for fabrication of ultra-shallow, hyper-abrupt, highly activated junctions for decananometer MOS transistors, Electrochem. Soc. Symp. Proc., vol. 2000-9, pp. 95-105, 2000.

- 9. B-Y Tsui and M-C Chen, Series Resistance of Self- Aligned Silicided Source/Drain Structure, IEEE Trans. Electron Devices 40, 197-206 (1993)

- 10. T. Uchino, T. Shiba, K. Ohnishi, A. Miyauchi, M. Nakata, Y. Inoue, and T. Suzuki, A Rasid Source/Drain Technology Using In-situ P-doped SiGe and B-doped Si for 0.1-μm CMOS ULSIs, IEDM 97-479

- 11. Y. Nakahara, K. Takeuchi, T. Tatsumi, Y. Ochiai, S. Manako, S. Samukawa, and A. Furukawa, Ultra-shallow in-situ-doped raised source/drain structure for subtenth micron CMOS, 1996 Symposium on VLSI 174 – 175

- 12. C. –P. Chao, K. E. Violette, S. Unnikrishnan, M. Nandakumar, R. L. Wise, J. A. Kittl, Q.-Z. Hong, and I.-C. Chen, Low Resistance Ti or Co Salicided Raised Source/Drain Transistors for Sub-0.13 μm CMOS Technologies, IEDM 97-103

- 13. C.M. Osburn, I. De, K.F. Yee and A. Srivastava, Design and Integration Considerations for End-of-the Roadmap Ultra-Shallow Junctions, J. Vac. Sci. Technol.B, 18 (1), 338 (2000)

- 14. Ming L. Yu and B. S. Meyerson, The adsorption of PH<sub>3</sub> on Si(100) and its effect on the coadsorption of SiH<sub>4</sub>, J. Vac. Sci. and Technol. A 2, 446 (1984)

- 15. Ming L. Yu and D. J. Vitkavage, B. S. Meyerson, Doping reaction of PH3 and B2H6 with Si(100), J. Appl. Phys. 59, 4032 (1986)

- 16. F. Hirose and H. Sakamoto, Thermal Desorption of surface phosphorus on Si (100) surfaces, Surf. Sci. 430, L540 (1999)

- 17. L. Kipp, R. D. Bringans, D. K. Biegelsen, J. E. Northrup, A. Garcia, and L. E. Swartz, Phosphine adsorption and decomposition on Si(100) 2x1 studied by STM, Phys. Rev. B63, 5843 (1995)

- 18. D. –S. Lin, T. –S. Ku, and T. –J. Sheu, Thermal reactions of phosphine with Si (100): a combined photoemission and scanning-tunneling-microscopy study, Surf. Sci. 424, 7 (1999)

- 19. D. S. Lin, T. S. Ku, and R. P. Chen, Interaction of phosphine with Si (100) from core-level photoemission and real-time scanning tunneling microscopy, Physical Review B 61, 2799 (2000)

- M. L. Colaianni, P. J. Chen, and J. T. Yates, Jr., Unique hydride chemistry on solocon-PH3 interaction with Si(100)-(2X1), J. Vac. Sci. and Technol. A 12, 2995 (1994)

- 21. J. Shan, Y. Wang, and R. J. Hamers, Adsorption and Dissociation of Phosphine on

- Si(100), J. Phys. Chem. 100, 4961 (1996)

- 22. M. Racanelli and D. W. Greve, In-situ doping of Si and Si<sub>1-x</sub>Ge<sub>x</sub> in ultrahigh vacuum chemical vapor deposition, J. Vac. Sci. and Technol. B 9, 2017 (1991)

- 23. S. -M. Jang, K. Liao, and R. Reif, Phosphorus doping of epitaxial Si and Si<sub>1-x</sub>Ge<sub>x</sub> at very low pressure, Appl. Phys. Lett. 63, 1675 (1993)

- 24. N. Maity, L. Q. Xia, and J. R. Engsrom, Effect of PH3 on the dissociative chemisorption of SiH<sub>4</sub> and Si<sub>2</sub>H<sub>6</sub> on Si (100): Implication on the growth of in-situ doped Si thin films, Appl. Phys. Lett. 66, 1909 (1995)

- 25. L. P. Chen, G. W. Huang, and C. Y. Chang, Phosphorus doping of Si and Si<sub>1-x</sub>Ge<sub>x</sub> grown by ultrahigh vacuum chemical vapor deposition using SiH<sub>4</sub> and GeH<sub>4</sub>, Appl. Phys. Lett. 68, 1498 (1996)

- X. D. Huang, P. Han, H. Chen, Y. D. Zheng, L. Q. Hu, R. H. Wang, S. M. Zhu, and

D. Feng, J. Vac. Sci. and Technol. B 14, 2690 (1996)

- 27. I. Ban and M. C. Öztürk, In situ phosphorus doping during silicon epitaxy in an ultrahigh vacuum rapid thermal chemical vapor deposition reactor, J. Electrochem. Soc. 146, 4303 (1999)

- 28. M.-H. Xie, J. Zhang, J. M. Fernandez, A. K. Lees, and B. A. Joyce, Surf. Sci. 397, 164 (1998)

- 29. J. A. N. T. Soares, H. Kim, G. Glass, P. Desjardins, and J. E. Greene, Arsenic-doped Si (001) gas-source molecular beam epitaxy: Growth kinetics and transport properties, Appl. Phys. Lett. 74, 1290 (1999)

- 30. J. H. Comfort and R. Reif, Plasma-enhanced chemical vapor deposition of in-situ

- doped epitaxial silicon at low temperatures, J. Appl. Phys. 65, 1053 (1989)

- 31. R. F. C. Farrow and J. D. Filby, J. Electrochem. Soc. 118, 149 (1971)

- 32. R. Malik, E. Gulari, P. Bhattacharya, K. K. Linder, and J.-S. Rieh, Very high (> 10<sup>19</sup> cm<sup>-3</sup>) in-situ n-type doping of silicon during molecular beam epitaxy using supersonic jets of phosphine, Appl. Phys. Lett. 70, 1149 (1997)

- 33. K. D. Hobart, F. J. Kub, G. G. Jernigan, and P. E. Thompson, Surface segregation of arsenic and phosphorus from buried layers during Si molecular beam epitaxy, J. Vac. Sci. and Technol. B 14, 2229 (1996)

- 34. V. G. Zavodinskii, Computer Study of Phosphorus Segregation Mechanisms at a SiO<sub>2</sub>/Si(100) Interface, Semiconductors 34, 296 (2000)

- 35. J. F. Nützel and G. Abstreiter, Comparison of P and Sb as n-dopants for Si molecular beam epitaxy, J. Appl. Phys. 78, 937 (1995)

- 36. S. Kobayashi, M. Iizuka, T. Aoki, and N. Mikoshiba, Segregation and diffusion of phosphorus from doped Si-Ge films into silicon, J. Appl Phys 86, 5480 (1999)

- 37. F. Hirose and H. Sakamoto, Prediction of concentration profile for P doping in Si gas-source molecular beam epitaxy, J. Crys. Growth 196, 115 (1999)

- 38. G. Lippert, H. J. Osten, D. Kruger, Phosphorus doping in molecular beam epitacial grown silicon and silicon/germanium using a GaP decomposition source, J. Crystal Growth 157, 304 (1995)

- 39. K. D. Hobart, D. J. Godbey, and P. E. Thompson, Sb surface segregation and doping in Si(100) grown at reduced temperature by molecular beam epitaxy, Appl. Phys. Lett. 63, 1381 (1993)

- 40. R.P.U. Karunasiri, G.H. Gilmer, and H.-J. Grossmann, Rate theory model of dopant incorporation during molecular beam epitaxy: effects of Coulomb repulsion, Surf. Sci. 317, 361 (1994)

- 41. K. D. Hobart, D. J. Godbey, M. E. Twigg, M. Fatemi, P. E. Thonpson, and D. S. Simons, Surface segregation and structure of Sb-doped Si(100) films grown at low temperature by molecular beam epitaxy, Surface Science 334, 29 (1995)

- 42. K. Kimura, Y. Endoh, M. Mannami, H. J. Gossmann, G. H. Gilmer, and L. C. Feldman, Anomalous surface segregation of Sb in Si during epitaxial growth, Appl Phys Lett 69, 67 (1996)

- 43. S. H. Li, P. K. Bhattacharya, S. W. Chung, J. X. Zhou, and E. Gulari, Solid Boron and Antimony doping of Si and SiGe Grown by Gas source Molecular Beam Epitaxy, J. Electronic Materials 22, 409 (1992)

- 44. J. M. C. Thoraton, R. J. Cole, D. J. Gravestejn, and P. Weightman, Donor activation and electronic screening at an antimony delta layer in silicon, Physical Review B 54, 7972 (1996)

- 45. K. D. Hobert, D. J. Godbey, P. E.Thompson, and D. S. Simons, Sb surface segregation during heavy doping of Si(100) grown at low temperature by molecular beam epitaxy, J. Vac. Sci. Technol B 11, 1115 (1993)

- 46. J. Ushio, K. Nakagawa, M. Miyao, and T. Maruizumi, Surface segregation behavior of Ge in comparison with B, Ga, and Sb: calculations using a first-principles method, J. Crystal Growth 201/202, 81 (1999)

- 47. E. Kasper and M. Oehme, Surface segregation determination by epitaxy

- temperature steps, Appl. Phys. Lett. 76, 3573 (2000)

- 48. H. Jorke, Surface Science 193, 569 (1988)

- 49. J. F. Nützel and G. Abstreiter, Segregation and diffusion on semiconductor surfaces, Physical Review B. 53, 13551 (1996)

- 50. A. Yamada, Y. Jia, M. Konagai, and K. Takahashi, Heavily P-doped (> 10<sup>21</sup> cm<sup>-3</sup>) silicon films grown by Photochemical Vapor Deposition at 250°C, J. Electronic Materials. 19, 1083 (1990)

- 51. H.-J Gossmann, F. C. Unterwald, and H. S. Luftman, Doping of Si thin films by low-temperature molecular beam epitaxy, J. Appl. Phys. 73, 8237 (1993)

- 52. J. F. Nützel, M. Holzmann, P. Schittenhelm, and G. Abstreiter, Segregation of n-dopants on SiGe surfaces, Appl. Surface Science 102, 98 (1996)

- 53. S. M. Celik and M.C. Öztürk, Low Thermal Budget In-situ Surface Cleaning for Selective Silicon Epitaxy, J. Electrochem. Soc. 145, 3602 (1998)

- 54. M. K. Sanganeria, K. E. Violette, M. C. Öztürk, G. Harri, C. A. Lee and D. M. Maher, Cleaning During Initial Stages of Epitaxial Growth Using Disilane in an Ultra-High Vacuum Chemical Vapor Deposition Reactor, Proceedings of the MRS symposium, 1993.

# Il Deposition of In-situ Phosphorus Doped Silicon-Germanium Alloys

Ban's results on phosphorus incorporation reviewed in Chapter I are typical of insitu phosphorus doped Si epitaxial layers [1]. While in-situ doped polycrystalline layers deposited at higher temperatures can reach phosphorus levels in excess of  $10^{20}$  cm<sup>-3</sup>, epitaxial layers are in general limited to concentration levels below this regime. Fortunately, higher phosphorus levels can be obtained in Si<sub>1-x</sub>Ge<sub>x</sub> alloys as discussed in Chapter I. This chapter examines in-situ P doped Si and Si<sub>1-x</sub>Ge<sub>x</sub> growth by UHV-RTCVD. The Si and Si<sub>1-x</sub>Ge<sub>x</sub> films were characterized by atomic force microscopy (AFM), secondary ion mass spectroscopy (SIMS), X-ray diffraction (XRD), and Hall-Effect measurements. In this work, we have used high resistivity (8-10 ohm-cm) and low resistivity (0.02 - 0.013 ohm-cm), 150 mm, p-type (100) silicon wafers.

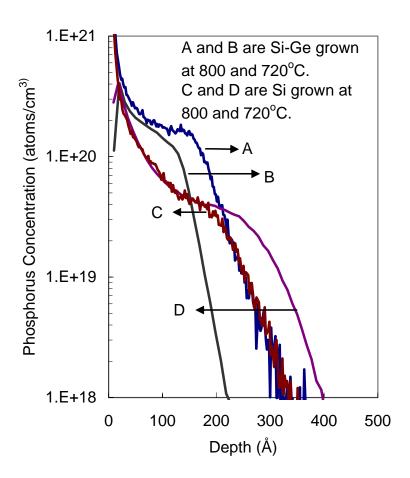

# II.1 Phosphorus Incorporation in Si<sub>1-x</sub>Ge<sub>x</sub>

Figure II.1 shows typical phosphorus profiles obtained in this work in heavily doped Si and Si-Ge epitaxial films. The phosphorus profiles "A" and "B" were obtained from Si<sub>1-x</sub>Ge<sub>x</sub> layers grown at 800°C and 720°C respectively. For comparison, C and D are from Si layers grown at the same temperatures. The detailed growth conditions for these samples and others prepared in this study are summarized in Table 2.1. As shown, addition of GeH<sub>4</sub> to the Si<sub>2</sub>H<sub>6</sub>-PH<sub>3</sub> chemistry provides a significant enhancement in phosphorus

incorporation. This is in agreement with previous work summarized in Chapter 1 [2-6]. As discussed, the presence of germanium retards P-P dimerization increasing the phosphorus concentration on the growth surface. Phosphorus can exist in the form of Si-P and Ge-P heterodimers.

Figure II.1 Phosphorus profiles of Si and Si<sub>1-x</sub>Ge<sub>x</sub> films obtained by SIMS.

Table 2.1 Deposition conditions used in the experiment to study the effects of temperature and GeH<sub>4</sub>/Si<sub>2</sub>H<sub>6</sub> ratio on growth rate and film properties.

| Samples | T (°C)    | 1% PH <sub>3</sub> (sccm) | 100% Si <sub>2</sub> H <sub>6</sub> (sccm) | 8% GeH <sub>4</sub> (sccm) | H <sub>2</sub> (sccm) | Total Pressure (mtorr) |

|---------|-----------|---------------------------|--------------------------------------------|----------------------------|-----------------------|------------------------|

| A       | 810       | 200                       | 10                                         | 37.5                       | 0                     | 100                    |

| В       | 720       | 200                       | 10                                         | 37.5                       | 0                     | 100                    |

| С       | 810       | 200                       | 12                                         | 0                          | 35                    | 100                    |

| D       | 720       | 200                       | 12                                         | 0                          | 35                    | 100                    |

| Е       | 830 - 670 | 140                       | 14                                         | 0                          | 0                     | 43                     |

| F       | 830 - 670 | 140                       | 12                                         | 37.5                       | 0                     | 74                     |

| G       | 830 - 670 | 140                       | 8                                          | 50                         | 0                     | 80                     |

|         | _         |                           |                                            |                            |                       |                        |

As discussed in Chapter 1, phosphorus atoms adsorbed on the Si surface form P-P dimers and desorb readily. Increasing the phosphine flow increases the density of adsorbed phosphorus atoms, which in turn enhances P-P dimerization and subsequent desorption. This is one of the reasons why increasing the partial pressure of phosphine does not result in a proportionate increase in phosphorus concentration. It has also been mentioned in Chapter 1 that phosphorus has a tendency to segregate to the surface during growth, which is responsible for the surface peak observed in Figure II.1. Surface segregation makes it more difficult to reach high concentrations in the Si<sub>1-x</sub>Ge<sub>x</sub> layer. Nevertheless, as shown in Figure II.1, the phosphorus concentration in both Si<sub>1-x</sub>Ge<sub>x</sub> layers is above 10<sup>20</sup> cm<sup>-3</sup>. The surface segregation may actually be helpful by providing a large amount of phosphorus to the metal - Si<sub>1-x</sub>Ge<sub>x</sub> interface, which is a key requirement for achieving low contact resistivity.

## **II.2** Growth Rate

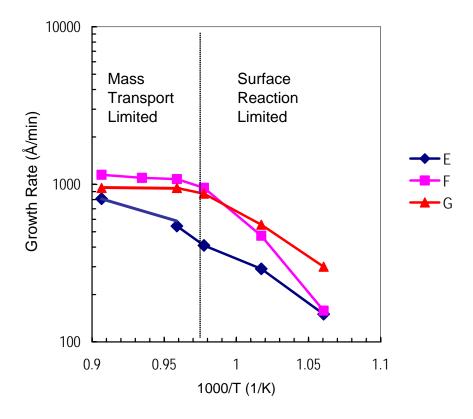

Figure II.2 Si and Si<sub>1-x</sub>Ge<sub>x</sub> growth rate with respect to inverse temperature.

Shown in Figure II.2 is the growth rate plotted as a function of inverse temperature obtained from samples E - G whose deposition conditions are given in Table 2.1. For the sample set E, one can conclude that the silicon growth rate is increasing with temperature in the entire temperature range considered. A straight line fit to sample set E yields an activation energy of ~18 kcal/ mol which is much lower than the reported activation energies for hydrogen and P-P dimer desorption (47 kcal/ mol and 200 kCal/ mol

respectively) [7]. On the other hand for sample sets F and G, the  $Si_{1-x}Ge_x$  growth rate appears to saturate above  $T \sim 750^{\circ}C$  indicative of mass transport limited growth. Below this temperature, the growth rate drops exponentially with temperature indicative of surface reaction limited growth. However, the number of data points is not sufficient to conclude if the growth is entirely controlled by the surface reactions. It is possible that a large portion of the temperature range includes the transition region between the two regimes and the growth rate may very well be limited by both mechanisms. Another complication arises from the fact that the Ge content of the epitaxial layers in Figure II.2 is also affected by the growth temperature. At lower temperatures,  $GeH_4$  can decompose more readily than  $Si_2H_6$ .

Table 2.2 Deposition conditions used in the experiment to study the effects of temperature and phosphine flow rate on growth rate and film properties. Same samples are also used to study resistivity, mobility and active carrier concentration.

| Samples | T (°C) | 1% PH <sub>3</sub> (sccm) | 100% Si <sub>2</sub> H <sub>6</sub> (sccm) | 8% GeH <sub>4</sub> (sccm) | H <sub>2</sub> (sccm) | Total Pressure (mtorr) |

|---------|--------|---------------------------|--------------------------------------------|----------------------------|-----------------------|------------------------|

| A       | 810    | 20 - 200                  | 16                                         | 50                         |                       |                        |

| В       | 760    | 20 - 200                  | 13.6                                       | 83.7                       |                       |                        |

| C       | 760    | 20 - 200                  | 10                                         | 125                        | variable              | 140                    |

| D       | 720    | 20 - 200                  | 13.6                                       | 83.7                       |                       |                        |

| E       | 720    | 20 - 200                  | 10                                         | 125                        |                       |                        |

Consequently, the Ge content is expected to increase as the temperature is reduced.

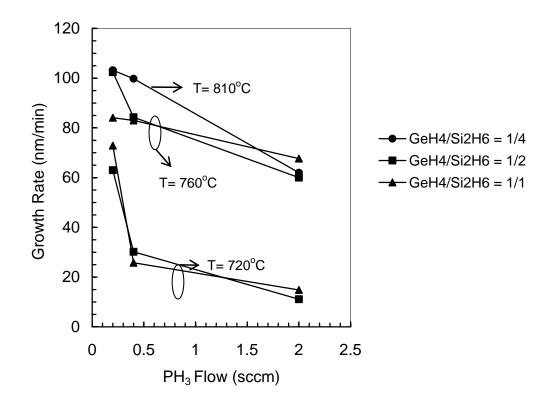

Shown in Figure II.3 is the growth rate as a function of the phosphine flow. The deposition parameters are included in Table 2.2. As expected,  $\mathrm{Si}_{1\text{-x}}\mathrm{Ge}_x$  growth rate decreases as the PH<sub>3</sub> flow increases in the temperature range considered. At 810°C, the growth rate decreases from 120 nm/min to 60 nm/min corresponding to a reduction of  $\sim$

50%. At 720°C, the reduction is more than 75%. It is interesting to note that at 760°C for the highest GeH<sub>4</sub>/Si<sub>2</sub>H<sub>6</sub> ratio of 1/1, PH<sub>3</sub> has a lesser impact on growth rate. However, variations in system conditions and/or measurement errors may be responsible for this behavior. Nevertheless, the general conclusion remains the same: PH<sub>3</sub> can significantly reduce the growth rate. The impact of temperature is also clear. A significant enhancement in growth rate is obtained by raising temperature from 720°C to 810°C. This is especially evident for higher PH<sub>3</sub> flows, which can be attributed to passivation of the surface adsorption sites at lower temperatures. It is interesting to note that 760°C is close to the temperature needed for P<sub>2</sub> desorption originating from P-P migrating mono-dimers in Figure I. [8]. P desorption from the Si-P hetero-dimers require  $\sim 850$ °C, hence, its contribution to P desorption should be small.

## II.3 Resistivity, Mobility and Carrier Concentration

Numerous samples were grown in the course of this study to determine the optimum growth conditions to maximize phosphorus incorporation in Si<sub>1-x</sub>Ge<sub>x</sub> layers. Samples were grown to study factors including temperature, gas flows, total pressure and film thickness. Because of these repetitive experiments and the large number of samples, it was not possible to employ Secondary Ion Mass Spectroscopy (SIMS) to analyze the samples due to high costs involved. As a partial solution, we have used Hall Effect measurements to study phosphorus incorporation in epitaxial layers. A 1000 Å thick thermal oxide layer on the silicon wafers was patterned by photolithography and wet etching to define active areas for clover shaped Van der Pauw structures.

Figure II.3 Si<sub>1-x</sub>Ge<sub>x</sub> growth rate as a function of PH<sub>3</sub> flow at various temperatures.

The Hall Effect measurement suffers from several sources of error in determining the phosphorus incorporation. First, as shown in Figure II.1 due to phosphorus segregation at the growth surface it is not possible to obtain a uniform phosphorus concentration in the grown layers. Thus, the active phosphorus level obtained from this type of measurement can only represent an average concentration. Furthermore, this corresponds to the average value of the *active* phosphorus distribution, which is expected to be varying with depth as suggested by the SIMS profiles shown in Figure II.1. Finally, in extracting the active phosphorus concentration, we assume a Hall scattering factor of unity for all grown layers,

which is most likely not true. The importance of Hall coefficient on the extraction process can be explained as follows: The expression for electron concentration is given by [9],

$$n = -\frac{r}{qR_H},$$